# DIGITER OF TUNNG FORK

## Dear Readers

The word "digital" is by no means new to you. "Digital" has been used to describe many things, from clocks to computers. It's as though the mere mention of the word created a spell-binding effect. No wonder sales promotion ad agencies make frequent use of the word!

In fact, today, digital technology has made its presence felt among audio products such as tape decks, turntables, tuners, etc. As a result, the products' features and functions as well as their quality and reliability have been greatly improved over conventional versions.

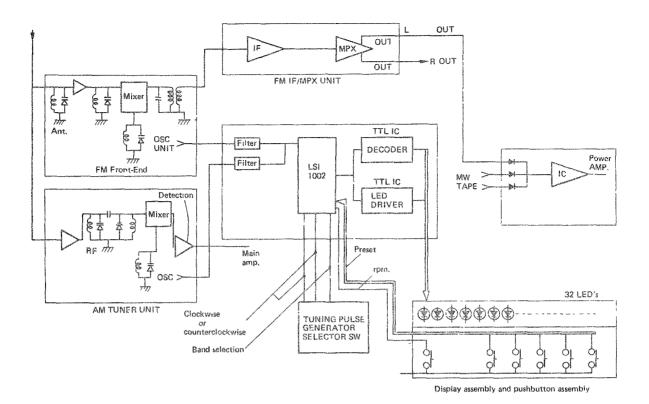

For instance, many relays and switches have been replaced by digital IC's which use the simple logic of 0 and 1, or ON and OFF in a pair. In control circuits, digital IC's have been employed for auto music selection, auto lead-in, return and repeat functions, etc. In Pioneer's high-end digital tuner, for example, digital technology has also been employed for automatic scanning, programmable preset tuning, electronic switching, LED and LCD display circuits and stable frequency performance.

There is no doubt that many new products to be released in the near future will make greater use of digital IC technology. With this in mind, Pioneer has prepared this book to help you understand the fundamental digital principles and to supplement the explanations in service manuals for Pioneer products featuring digital technology.

There are many things to be learned before acquiring a complete understanding of "digital," and it is our hope that this book will be helpful in your study.

## Contents\_\_\_\_\_

| Basic Course "Digital"                 | 1        |

|----------------------------------------|----------|

| 1. Digital and analog                  | 1        |

| 2. Logic circuit                       | 1        |

| 1. Types of circuits                   | 1        |

| 2. Positive and negative logic         | 4        |

| 3. Digital IC's                        | 8        |

| 1. Types of digital IC's               | 8        |

| 2. Density of integration and packages | 8        |

| TTL IC primary course-threshold level  | 9        |

| 3. TTL IC                              | 11       |

| 4. CMOS IC                             | 13       |

| 4. Gate combinations                   | 17       |

|                                        | 17       |

| 2. Multistage gate connections         | 18       |

| 3. Circuit employing gates             | 19       |

| 5. Flip-flop                           | 23       |

|                                        | 23       |

|                                        | 24       |

|                                        | 24       |

|                                        | 28       |

|                                        | 30       |

| 5 x                                    | 30       |

|                                        | 31       |

| •                                      | 31       |

|                                        | 33       |

|                                        | 33       |

|                                        | 33       |

|                                        | 34       |

|                                        | 35       |

|                                        | 36       |

|                                        | 36       |

|                                        | 38       |

|                                        | 30       |

| Application Course (1) CT-F750         | 39       |

| 1. Control circuit's functions         |          |

|                                        | 39       |

|                                        | 39<br>40 |

|                                        | 41       |

|                                        | 42       |

|                                        | ₹∠<br>42 |

|                                        | 43       |

|                                        | 43<br>44 |

|                                        | 45       |

|                                        | 45<br>46 |

|                                        | 40<br>46 |

| • • •                                  | 40<br>47 |

|                                        | 47<br>48 |

| 9. Bias oscillator controller and      | -+0      |

|                                        | 49       |

| muting signal detector                 | 40       |

| 3. Troubleshooting Digital IC's                                                                                               | 50<br>50<br>50        |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------|

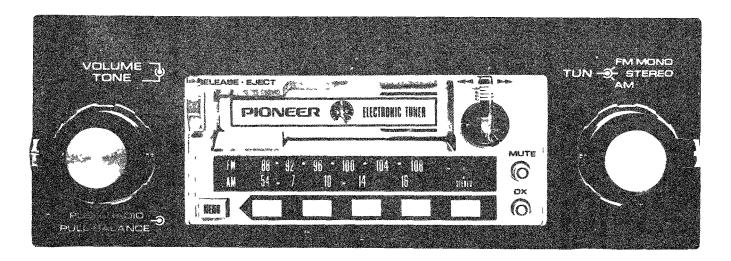

| Application Course (2)         KE-2000           1. KE-2000                                                                   | <b>56</b><br>56<br>57 |

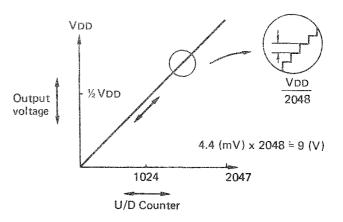

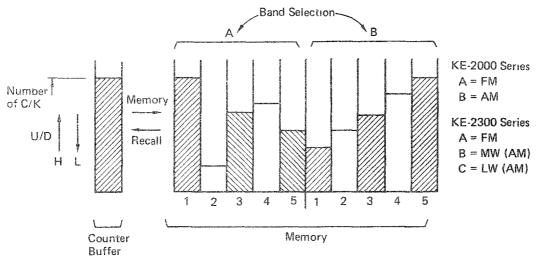

| 2. Up/down counter 3. Generation of voltage 4. Memory counter                                                                 | 58<br>58<br>59        |

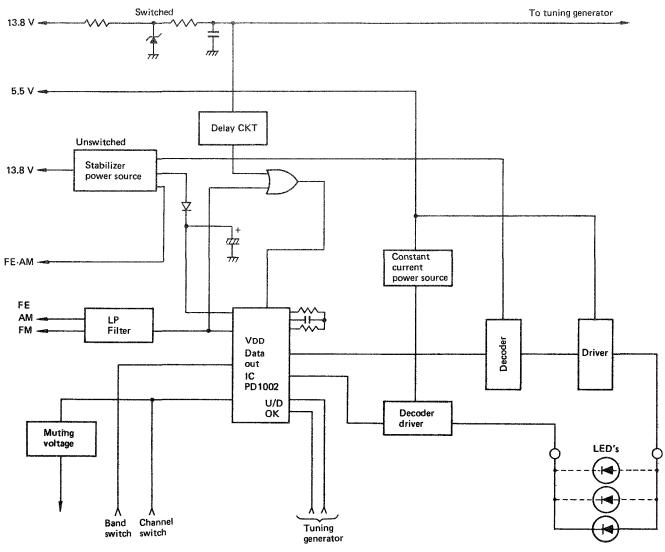

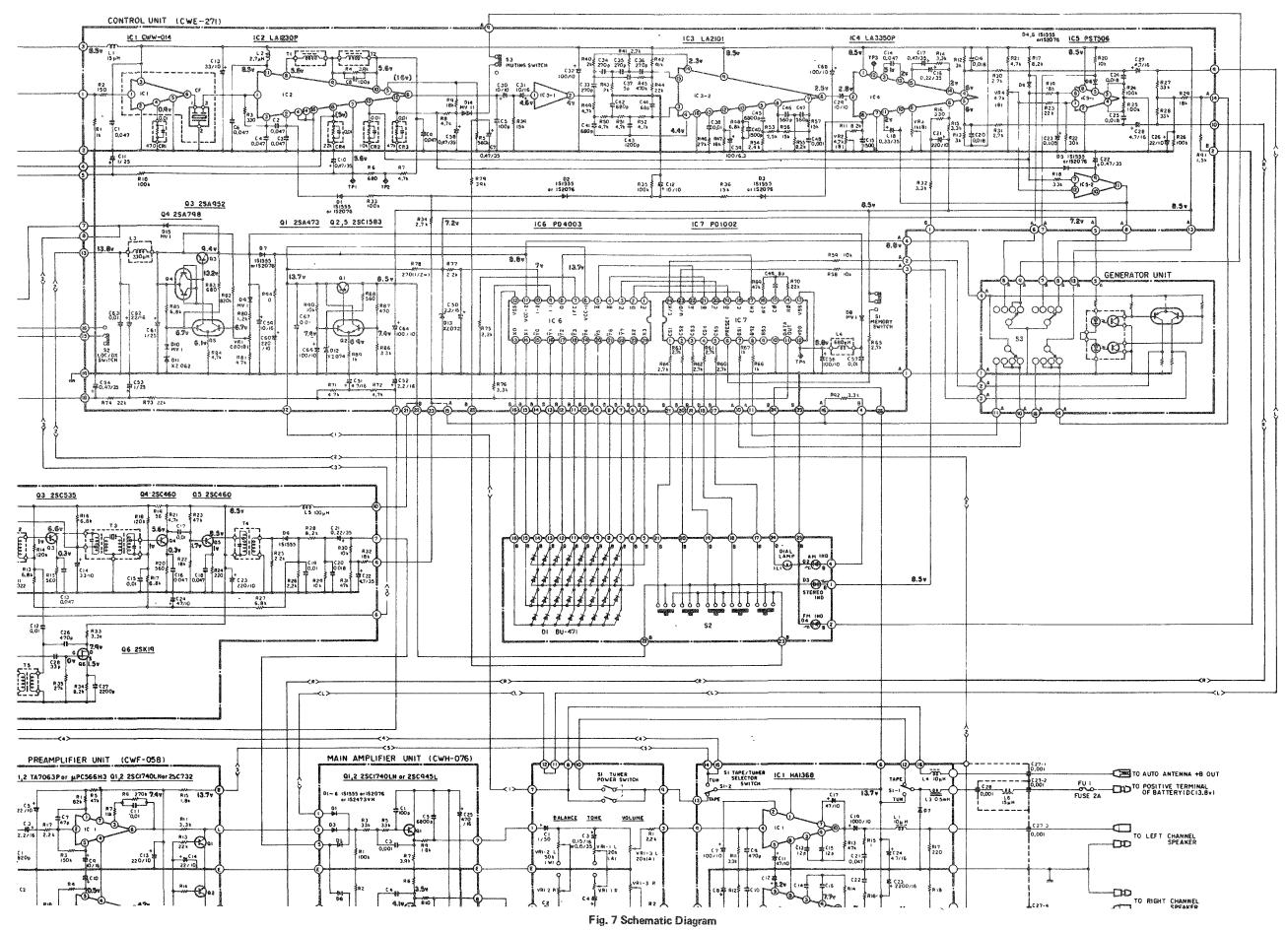

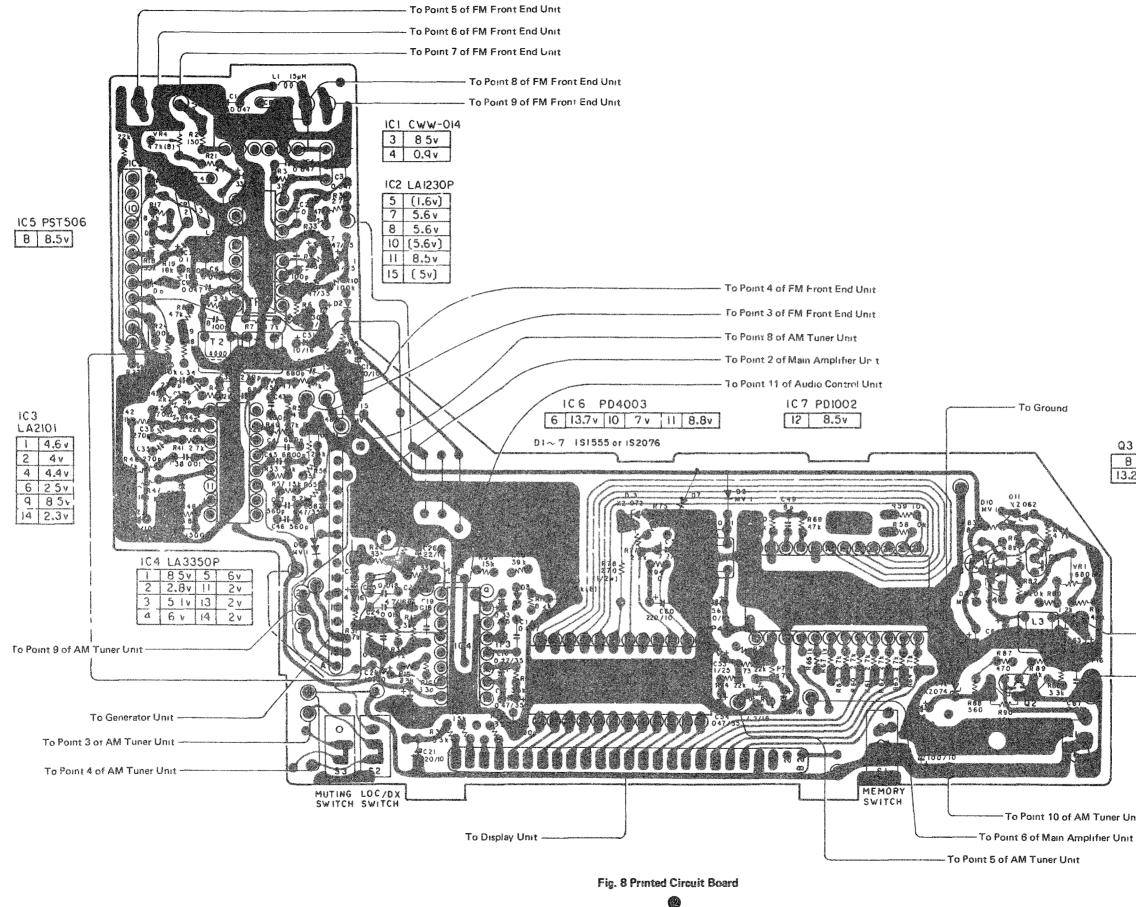

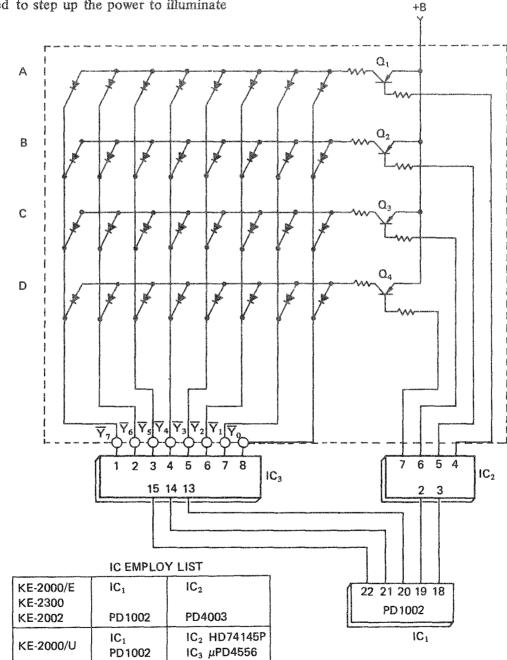

| <ol> <li>5. LED's for station indication</li> <li>2. Control circuit</li> <li>1. Control circuit</li> </ol>                   | 59<br>60<br>60        |

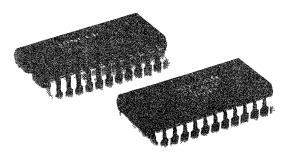

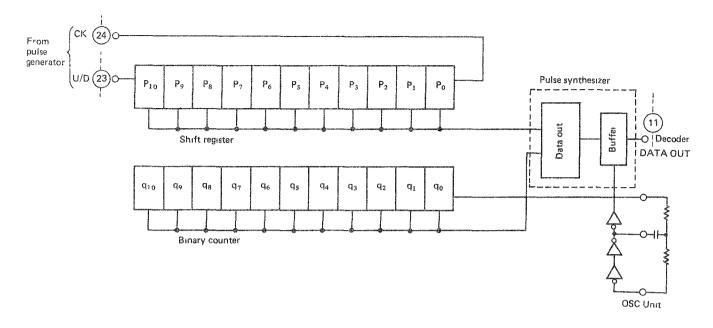

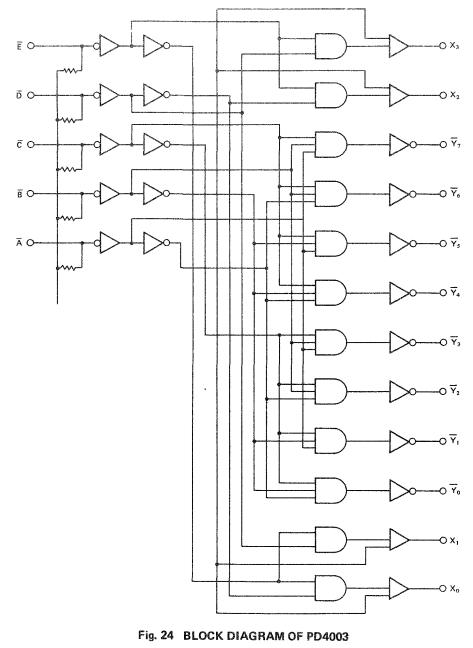

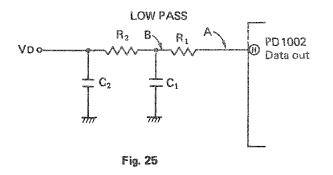

| 2. IC PD 1002         3. Circuit functions         1. Binary counter                                                          | 63<br>64<br>64        |

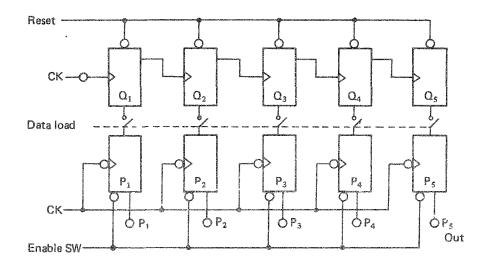

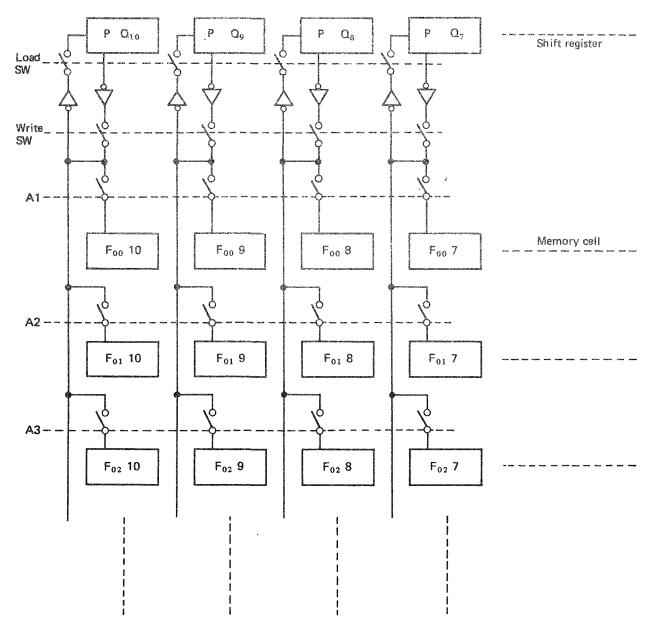

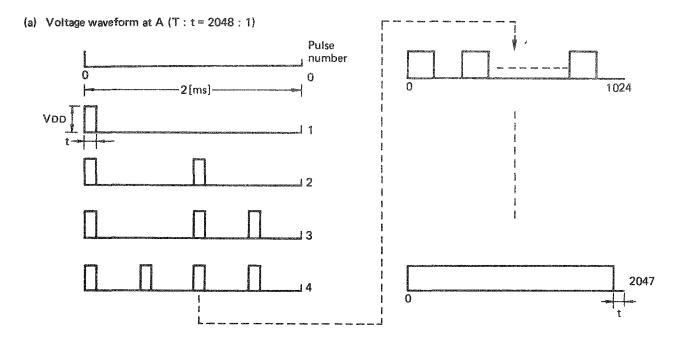

| 2. Binary up/down counter         3. Memory buffer (shift register)         4. Memory read/write         5. Pulse synthesizer | 65<br>67<br>68<br>71  |

| 6. Oscillator circuit                                                                                                         | 73<br>74<br>76        |

| 9. Troubleshooting                                                                                                            | 77<br><b>79</b>       |

| 1. Boolean algebra                                                                                                            | 79<br>79<br>80<br>81  |

| 5. Principle of duality                                                                                                       | 82                    |

# Basic Course "Digital"

#### 1. Digital and analog

The quantity of countable things, like trees or cars, can be determined by counting them digitally. On the other hand, uncountable things, such as water or time, must be measured analogically to determine their volume. Digital data is comprised of discrete units which have no intermediate value. If medium quantity is undesirable or inconvenient, digital processing is very effective.

The ordinary household light switch and thermostat whose positions or values are changeable in discrete steps, are digital circuits.

Diodes and transistors also work as digital switches.

#### 2. Logic circuit

In a logic circuit, the numbers 1 and 0 are used. These numbers in themselves do not indicate values but opposite states, such as "yes" and "no," "on" and "off," or "high" and "low." By using 1 and 0, the shifting process of all logic circuits can be understood and expressed in a logical algebraic form. (See appendix on Boolean Algebra.)

#### 2-1. Types of circuits

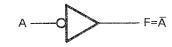

a) NOT circuit (Inverter)

NOT circuits are shown in Fig. 1 (a) and (b).

When the input of the circuit becomes 1, the output becomes 0, and when the input becomes 0, the output becomes 1 as shown on the truth table in Fig. 1 (c).

The circles in the symbols indicate negation, which will be explained later.

The function of a NOT circuit can be expressed algebraically by  $F = \overline{A}$ ,  $\overline{A}$  standing for negative A.

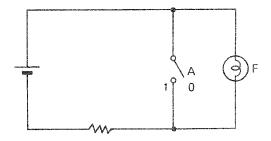

The lamp circuit shown in Fig. 1 (d) illustrates a simple example of a NOT circuit.

Supposing that:

| Switch A is closed | :A = 1 |

|--------------------|--------|

| Switch A is open:  | A = 0  |

| Lamp is on:        | F = 1  |

| Lamp is off:       | F = 0  |

Then, as the circuit clearly shows, the switch is open when the lamp is on. This proves that A and F are reversed as in the truth table in Fig. 1 (c).

(c) Truth table

| Α | F=Ā |

|---|-----|

| 1 | 0   |

| 0 | 1   |

(d) Light switching circuit

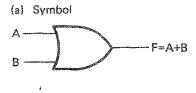

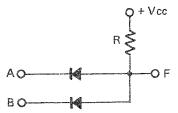

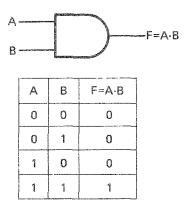

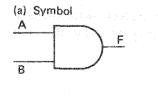

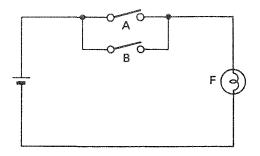

b) AND circuit (Logical multiplication)

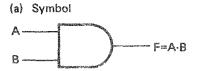

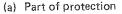

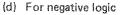

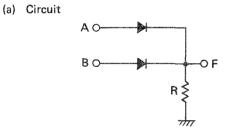

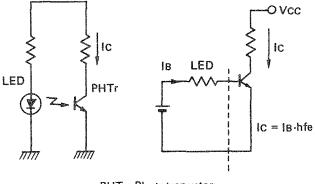

A typical AND circuit is snown in Fig. 2.

With two inputs, there are four combinations. Since the output becomes 1 only when the inputs are 1, the function can be expressed by  $F = A \cdot B$ .

Now let's apply this to the lamp cucuit.

The lamp will go on only when both A and B are 1. This can be determined by multiplying A and B as shown in the Fig. 2 (b) truth table.

Such a relationship between A and B is called logical multiplication, or AND, and such a circuit is known as an AND circuit.

(b) Truth table

| A | В | F=A·B |

|---|---|-------|

| 0 | 0 | 0     |

| 0 | 1 | 0     |

| 1 | 0 | 0     |

| 1 | 1 | 1     |

#### (c) Light switching circuit

#### Fig. 2 AND circuit

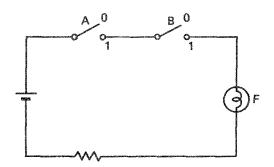

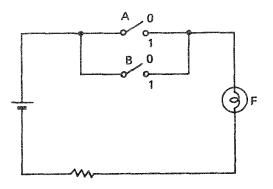

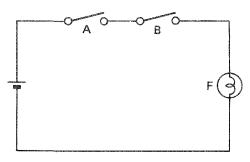

c) OR circuit (Logical addition)

This type of circuit is illustrated in Fig. 3.

With this circuit the output becomes i when at least one input is 1.

This junction is expressed as P = A - B.

Applying this to the lamp circuit  $n_{c}$  Fig. 3 (c), the lamp with be on when A or B is 1. In other words, this is determined by adding A and B as shown in the truth table in Fig. 3 (b).

(b) Truth table

| A | В | F=A+B |

|---|---|-------|

| 0 | 0 | 0     |

| 0 | 1 | 1     |

| 1 | 0 | 1     |

| 1 | 1 | 1     |

(c) Light switching circuit

Fig. 3 OR circuit

#### d) NAND circuit

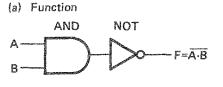

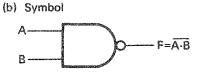

A NAND circuit is shown in Fig. 4.

This is a combination of an AND circuit and a NOT cucult.

As output F is the reverse of the AND circuit's output A·B, it is represented by  $\overline{AB}$ , the symbol for which is shown in Fig 4 (b).

The truth table in Fig. 4 (c) indicates that output F is the reverse of AND.

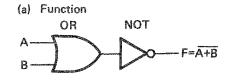

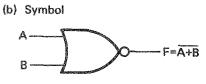

e) NOR circuit

Fig. 5 shows a NOR circuit, which is a combination of an OR and a NOT circuit.

As output F is the reverse of the OR circuit's A + B output. it is represented by  $\overline{A + B}$ , the symbol for which is shown in Fig. 5 (b).

The truth table in Fig. 5 (c) indicates that output F is the reverse of OR.

(c) Truth table

| <br>А | В | F= <del>Ā</del> ∙B |

|-------|---|--------------------|

| <br>0 | 0 | 1                  |

| 0     | 1 | 1                  |

| <br>1 | 0 | 1                  |

| 1     | 1 | 0                  |

(c) Truth table

| Α | В | F=A+B |

|---|---|-------|

| 0 | 0 | 1     |

| 0 | 1 | 0     |

| 1 | 0 | 0     |

| 1 | 1 | 0     |

Fig. 5 NOR circuit

#### 2-2. Positive and negative logic

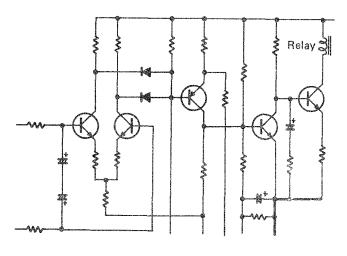

A logic circuit sounds very complicated. But Pioneer products already have circuits such as the one shown in Fig. 6. Since years ago, when the words "digital circuit" were not popular, we have been reading conventional circuits in the logical way.

Fig. 6 Typical protection circuit

When the voltage level at the base of a NPN (PNP) transistor becomes high, the level at the collector becomes low (high). Fig. 7 shows part of the protection circuit in Fig. 6, while Fig. 7 (b) shows its function table.

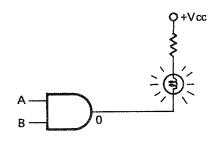

When both input levels become high (VCC: supplied voltage), the output level becomes high. When these high and low (0V) levels correspond to 1 and 0 respectively, this given is becomes an AND circuit, Fig. 7 (c). When these high and low levels correspond to 0 and 1 respectively, the function becomes that of an OR circuit, Fig. 7 (d). The logical function of a circuit changes completely when the level correspondents are shifted. The former (H = 1 and L = 0) is called "positive logic" and the latter (H = 0 and L = 1), "negative logic."

The circles at the terminal of Fig. 7 (d) indicate negative logic. Circuit (d) is an Invert NOR type, having negation circles at both input and output.

(b) Function table

| А  | В | F |        |

|----|---|---|--------|

| L  | L | L | H≒Vcc  |

| ۰L | Н | L | L≓0V   |

| Н  | L | L | L .0 V |

| Н  | Н | Н |        |

(c) For positive logic

| Ā | B | $F = \overline{\overline{A} + \overline{B}}$ |

|---|---|----------------------------------------------|

| 1 | 1 | 1                                            |

| 1 | 0 | 1                                            |

| 0 | 1 | 1                                            |

| 0 | 0 | 0                                            |

Fig. 7 Logic circuit

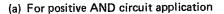

When positive logic 1 is applied to the input of the NOT circuit in Fig. 1 (a), the output becomes negative logic 1. The NAND circuit in Fig. 8 (a) can be considered an AND circuit with positive input logic and negative output logic. The circuit is the same as that shown in Fig. 4 (b).

Then positive logic 1 is applied to inputs A and B, the output becomes negative logic 1. When the output of the above is expressed in negative logic, the truth table will be the same as that of an AND circuit. Why should the same level be regarded differently? The answer is that it is easy to understand a whole circuit when the state of "lighting lamp" or "rotating motor" is expressed as 1 in Fig. 9 where the positive logic AND circuit shows that the lamp lights when the output is 0, which is hard to understand.

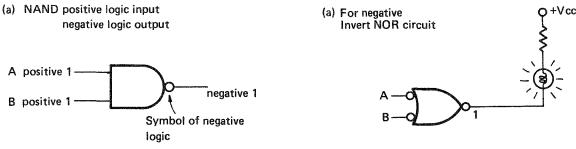

In Fig. 10, it is expressed with the negative logic Invert NOR circuit. With this circuit, it is easier to understand the function (refer to Fig. 11) that causes the lamp to light when one of the inputs is 1 (negative logic). The fact that a circuit can be considered to function as either an AND circuit or an OR circuit by positive or negative logic respectively is called "logical relativity."

(b) Truth table

| A | В | Ou | tput |

|---|---|----|------|

| 0 | 0 | 0  | ON   |

| 0 | 1 | 0  | ON   |

| 1 | 0 | 0  | ON   |

| 1 | 1 | 1  | OFF  |

(b) Truth table

| Pos<br>Iogi | itive<br>c | Negative<br>logic |

|-------------|------------|-------------------|

| A           | В          | F                 |

| 0           | 0          | 0                 |

| 0           | 1          | 0                 |

| 1           | 0          | 0                 |

| 1           | 1          | 1                 |

Fig. 8 NAND circuit

(b) Truth table

| Α | В | Output |     |

|---|---|--------|-----|

| 1 | 1 | 1      | ON  |

| 1 | 0 | 1      | ON  |

| 0 | 1 | 1      | ON  |

| 0 | 0 | 0      | OFF |

Fig. 10 Invert NOR circuit

These examples explain why there is both positive and negative logic for the same function.

Then, what about actual repair of a product or checking its operation? In this case, H (high) and L (low) levels are used, rather than the truth table, for checking voltage and wave forms.

The numbers 1 and 0 are useful when considering digital circuits logically, but a function table is more convenient for repairing.

Now let's see how the functions of each logic circuit can be easily understood from a circuit diagram that contains negative logic symbols.

In Table 1, the positive logic can be represented by H and the negative logic (marked with 0) by L. So let's use a NAND circuit (positive logic input) and an Invert OR circuit (negative logic input) and see what happens.

(1) NAND circuit

As the input is positive logic, it is represented by H; and the output, negative logic, by L. As the symbol is NOT + AND (AND + NOT), F = L when A and B =

H. This is represented by

ABF

H | H | L

in the function table.

(2) Invert OR circuit

As the input is negative logic, it is represented by L, and the output, positive logic, by H. As the symbol is NOT + OR, F = H when A or B = L. This is represented by

| А | B | F |

|---|---|---|

| L | L | Η |

| L | Н | Н |

| Н | L | Η |

in the function table.

Thus, a part of the function is represented by a symbol. As these logic circuits are generally termed gates, we will refer to them as such from here on (a NAND circuit = a NAND gate).

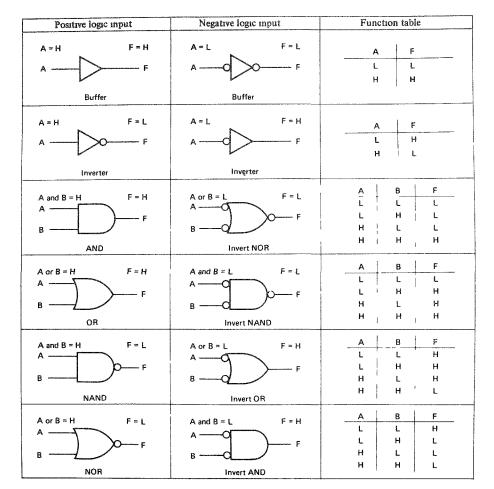

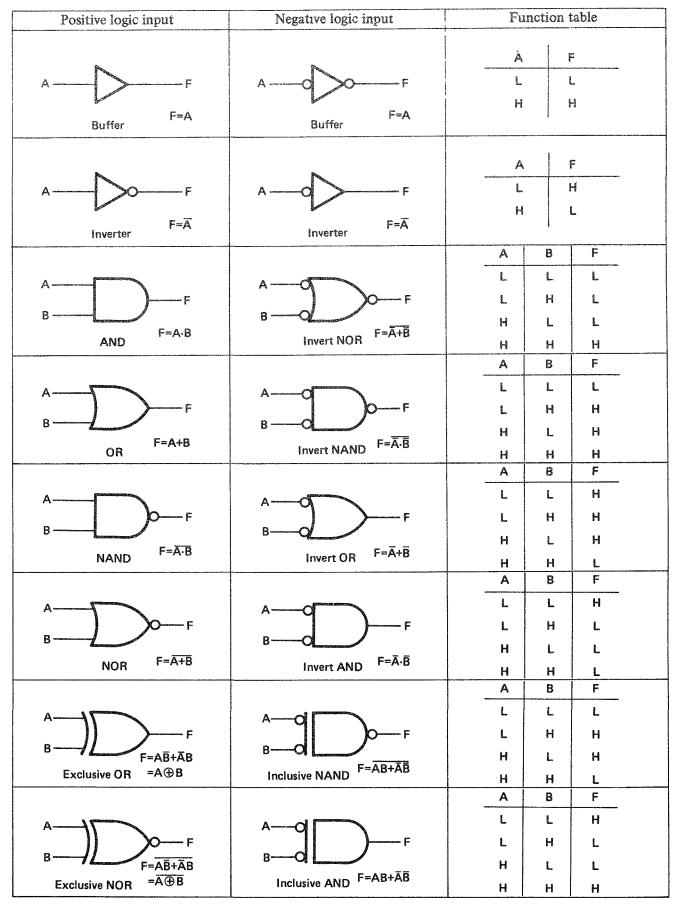

Table 2 shows various gates most frequently used. Please refer to 4-3i for the Exclusive OR circuit explanation.

Table 1 Conversion table

Table 2 Gate variations

Ø

#### 3. Digital IC's

#### 3-1. Types of digital IC's

Digital IC's can be classified by structure as follows: bipolar type using transistors and unipolar type using MOS FET's.

These two types can be further broken down into:

#### (a) Bipolar type

- \*RTL (Resistor-Transistor Logic) Old type not in use now.

- \*DTL (Diode-Transistor Logic) Scarcely used now.

- \*TTL (Transistor-Transistor Logic) The current mainstay type.

- \*ECL (Emitter-Coupled Logic) or CML (Current Mode Logic) an expensive, high-speed type.

- \*I<sup>2</sup> L (Integrated-Injection Logic) or MTL (Merged-Transistor Logic) A super-high-speed, high-density type. Expected to be the future mainstream type.

- (b) Unipolar type

- \*PMOS (P-channel MOS FET)

This was used in early-type LSI (large scale integration). It is still used in custom-made LSI's.

- \*NMOS (N-channel MOS FET) Widely used in present-day LSI.

- \*CMOS (Complementary MOS FET) Most widely used at present in various components from ordinary gates to custommade LSI.

The bipolar type generally responds quickly, though it consumes a considerable amount of power, while the unipolar type has a relatively slower response time and consumes less power. Since audio equipment does not require high speed, the less power consuming unipolar type is widely used.

As bipolar IC's are mostly TTL type and unipolar mostly CMOS type, these two will be explained in detail here; the others we will leave for another occasion.

#### 3-2. Density of integration and packages

As the number of elements (the number of gates) contained in a single package differs widely, IC's are classified by the density of integration of their elements. However, this classification is not rigid, differing from maker to maker.

a) SSI (Small Scale Integration) Number of elements: Less than 100 Number of gates: Less than 12

- b) MSI (Medium Scale Integration)

- Number of elements: 100 or more and less than 1,000

Number of gates: 12 or more and less than 100

c) LSI (Large Scale Integration) Number of elements: 1,000 or more Number of gates: 100 or more

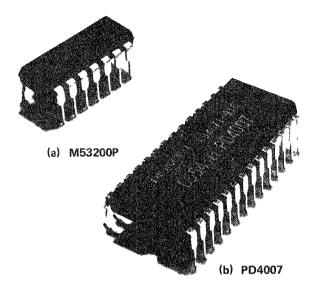

As for the package, digital IC's used in audio products are mostly plasticmolded DIP (dual-inline package) type. The photo (a) shows a NAND gate TTL IC with 14 terminals (14P), while (b) illustrates a 28P custom-made CMOS IC.

There is also a flat type, which is widely used in watches and clocks, as well as for industrial and military applications.

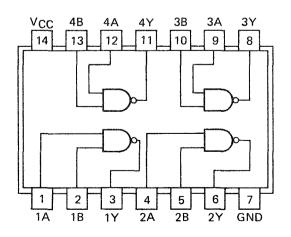

A gate IC contains several gates within a single package.

Fig. 11 SN7400N pin assignment (top view)

### TTL IC Primary Course — Threshold level

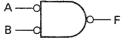

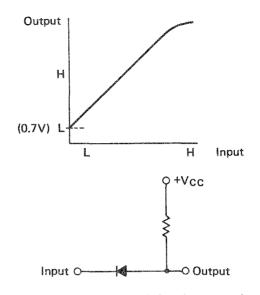

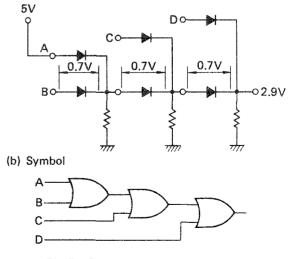

A circuit with two diodes and a resistor has logic functions. The circuit depicted in Fig. A (a), which is similar to that in Fig. 7 (a), functions as an OR gate by positive logic and as an INVERT NAND gate by negative logic. Threshold voltage level for shifting from 1 to 0 or 0 to 1 is determined by the forward rising voltage characteristics of a diode. But, actually, the level varies gradually [Fig. B] and no threshold can be found even if the input impedance is 0 and output load impedance is infinite. There would be no problem if a discrete level of 0V or VCC were applied to the input. But, when gates are connected in series [Fig. C], the combined circuit does not function.

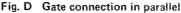

Even when the input of the gate 1 is 0V, the output of Gate 3 becomes 2.1V (0.7V + 0.7V + 0.7V). The minimum voltage required to make a current run through a diode is about 0.7V. The more stages, the harder it is to function as shown in Fig. C. With the circuit of Fig. D (a), a high input level of 5V decreases down to 2.9V at output. When threshold level is not discrete, logical judgement of 1 or 0 becomes difficult if the number of stages increases. The ideal input-output characteristics of an AND or OR gate are shown in Fig. E. The output voltage should change when the input becomes Vcc/2 and the difference between high and low levels should be large at input.

(b) Symbol

Positive logic

Fig. A Logic circuit with diodes and a resistor

Fig. B Input-output characteristics of a gate made of a diode and a resistor

(a) Circuit +Vcc +Vcc +Vcc Gate 1 Gate 2 Gate 3 0.7 n 7 0 7V Out 2.1V 7/17/ BO Co no (b) Symbol Δ D Fig. C Gate connection in series

Fig. E Output-input characteristics

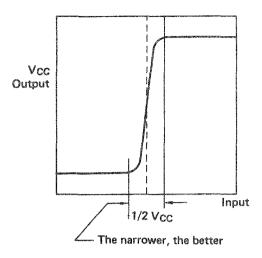

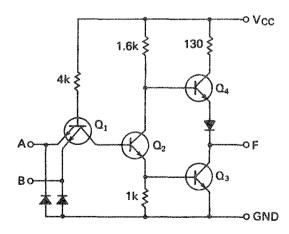

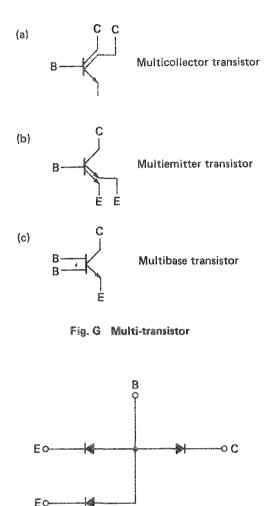

As you see, there are problems with gates which are made of diodes and resistors. To overcome the ambiguous threshold and output level differences between H and L, RTL, DTL, TTL, etc. have been developed utilizing transistors for switching functions. However, a gate has other characteristics such as delay time or response time and FAN OUT or the number of gates which can be connected to a single output. Today, TTL's are more popular for these applications. Fig. F is the circuit of a TTL NAND gate. In the figure you see an unfamiliar transistor  $Q_1$ . This is called a "multiemitter transistor"; one of the multitransistors shown in Fig. G, it is often used in digital and analog IC's. Its equivalent circuit is shown in Fig. H.

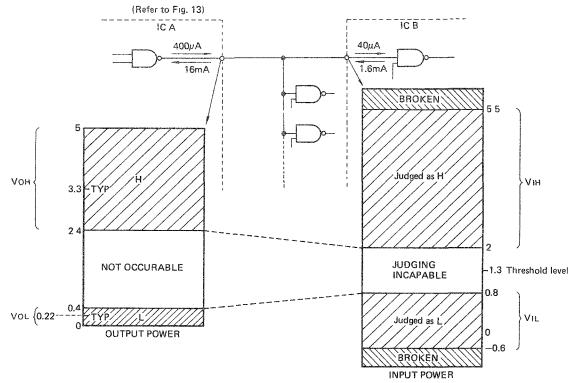

Input/output voltages of TTL IC's should be remembered when checking circuits which employ TTL IC's, or checking IC circuits will be impossible. Refer to Fig. 15.

Fig. F Basic circuit of TTL NAND gate

Fig. H Equivalent circuit of multiemitter transistor

#### 3-3. TTL IC

The original source of a TTL IC is the SN74 series circuit of Texas Instruments (TI). Currently, semiconductor makers are producing IC's with similar standards as second sources.

This chapter will deal with the standard type. For your reference, the following table shows their power consumption per gate and propagation delay time.

| Туре                         | Power<br>consumption | Propagation delay time |

|------------------------------|----------------------|------------------------|

| 74 (Standard)                | 10mW                 | 10nS                   |

| 74L (Low power)              | 1mW                  | 40nS                   |

| 74H (High speed)             | 22mW                 | 6.5nS                  |

| 74S (Schottky)               | 19mW                 | 3nS                    |

| 74LS (Low-power<br>Schottky) | 2mW                  | 10nS                   |

Table 3 Power consumption per gate/propagation delay time

Now let's go into the electric characteristics of TTL IC's.

a) Absolute maximum ratings

These are the maximum values permissible. Any change in condition which increases the stipulated value, even if it is instantaneous, will cause breakdown or deterioration of the TTL IC.

| Supply voltage:            | 7V                 |

|----------------------------|--------------------|

| Input voltage:             | $-0.5 \sim +5.5 V$ |

| Storage temperature range: | −55 ~ +150°C       |

b) Recommended operating condition

This is the necessary condition for obtaining the following performance.

|                  | Min. | NOR | Max. |

|------------------|------|-----|------|

| Operating supply |      |     |      |

| voltage (V):     | 4.75 | 5   | 5.25 |

| Fan-out*:        |      |     | 10   |

| Operating        |      |     |      |

temperature (°C): 0 25 70 \*Fan-out: The number of parallel-connected gates that can be driven by a single gate.

- c) Electrical characteristics

- (1) Input voltages

This is the voltage limit which can maintain output logical states (H or L).

H level input voltage VIH: 2V (min.). This is the minimum input voltage level which can maintain positive logic output of L.

L level input voltage VIL: 0.8V (max.). Maximum input level which can maintain positive logic output of H.

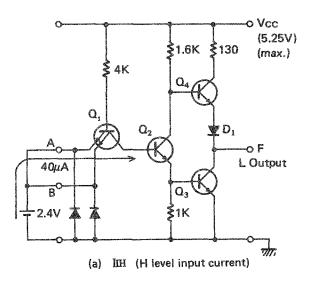

(2) Input current

This is the input current at the time Vcc max. is applied to the input.

The current varies in proportion to that of the supply voltage.

H level input current IIH: 40µA (max.)

Condition:  $V_{CC} = (max.) V_{IN} = 2.4V$

L level input current IIL : -1.6mA (max.)

This (-) symbol means that the current is flowing out.

Condition:  $V_{CC} = (max.), V_{IN} = 0.4V$

Fig. 12 shows the input current measuring conditions. Under these conditions, the input current is at its max.

Fig. 12 Measuring condition of input current

Ð

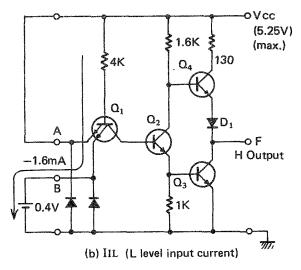

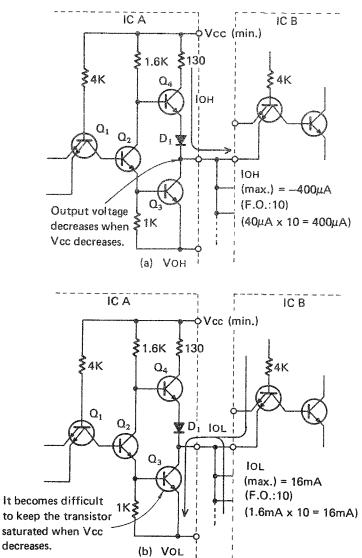

#### (3) Output voltages

These also vary according to the power supply voltage  $(4.75 \sim 5.25 \text{V})$ . It is the value of the time when the minimum operatable supply voltage is applied, because when the supply voltage decreases, the transistor base current decreases and this occurs even when the output is L, making it difficult to keep the state of the transistor saturated.

H level output voltage VoH: 2.4V (min.), 3.3V (TYP)\*

Condition: Vcc = (min.); VIN =

$$0.8V$$

, IOH =  $-400\mu A$

L level output voltage VoL: 0.4V (max.), 0.22V (TYP)

Condition:

$$Vcc = (min.); VIN = 2.4V, IOL = 16mA$$

Fig. 13 shows the measuring condition which makes the output voltage worst, or minimum, and indicates the direction of the output current.

Fig. 13 Measuring condition of output voltage

#### (4) Propagation delay time

The propagation delay time of a TTL IC is determined by the inner circuit being free from external interference. That of a NAND gate SN7400 is 10ns. The most influential load capacitance to produce a time delay of 6ns/100PF is determined by the following formula.

Propagation delay time:  $t_{pd} = (10 + 0.06CL)$ ns CL : load capacitance (pF)

#### (5) Power consumption

The power consumption of a gate is 5mW when the output level is H, and 15mW when it is L. This makes the average 10mW.

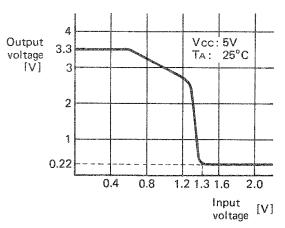

#### (6) Input/output characteristic

The input/output voltage characteristic of a TTL IC is shown in Fig. 14. The threshold voltage at a normal temperature TA of  $25^{\circ}$ C will be around 1.3V.

\* TYP stands for typical value.

Fig. 14 Characteristic of input voltage vs. output voltage

## Fig. 15 shows the input/output voltage range of a TTL IC.

Fig. 15 Voltage range of input and output of TTL IC

#### 3-4. CMOS IC (Complementary Metal Oxide Semiconductor IC)

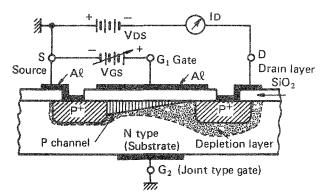

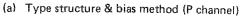

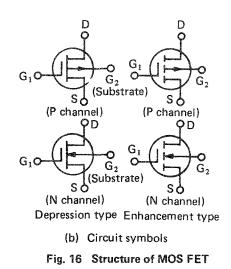

#### a) MOS-FET

Transistors currently being used are bipolar and FET type. The former is simply called "transistor," being used in popular amplifiers or TTL IC's. The latter can be subdivided into JFET (junction type, popularly employed in low-noise amplifiers) and MOS type. The MOS type consists of aluminum, SiO<sub>2</sub> and a semiconductor as shown in Fig. 16. Resistance between drain and source can be controlled in the range between  $10^2\Omega$  (ON) and  $10^{10}\Omega$  (OFF) by varying the voltage between the gate and source and by varying the current channel width.

The differences between the bipolar type transistor and MOS FET's are:

| Bipolar transistor      | MOS FET                    |

|-------------------------|----------------------------|

| (1) Base current flows. | Base current is very small |

|                         | because of insulated gate. |

|                         | Voltage-controlled type.   |

| (2) Saturation voltage  | When ON, drain and source  |

| remains.                | are in ohmic contact.      |

|                         | No saturation voltage re-  |

|                         | mains.                     |

#### b) CMOS logic circuit

In MOS FET's, there are P-channel and N-channel complementary types just like bipolar transistors. An IC which has both P-channel and N-channel MOS FET's on one substrate is called a CMOS IC. How, then, can we combine CMOS FET's in composing a logic circuit?

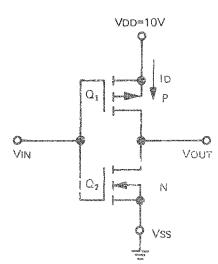

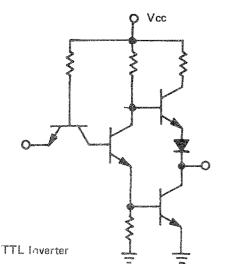

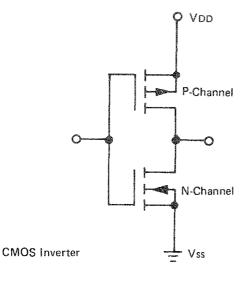

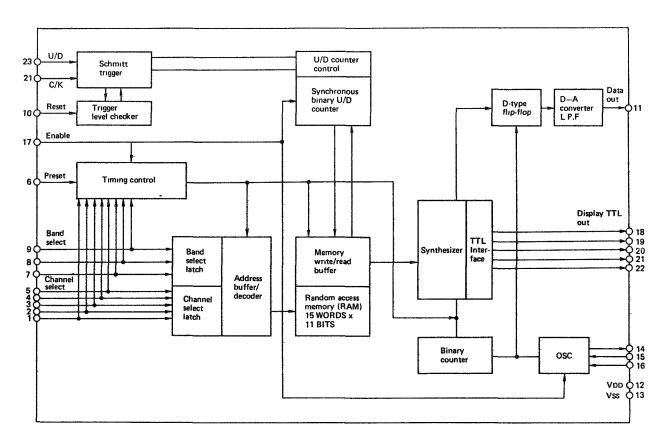

Fig. 17 shows an inverter which is a fundamental CMOS logic circuit.

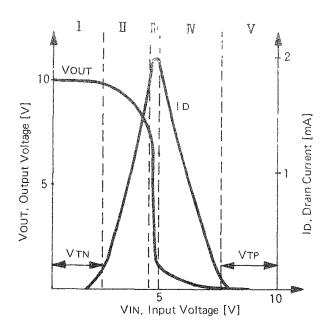

Fig. 18 shows its input/output and power supply current characteristics.

Note that the threshold is about 1/2VDD, "L" and "H" levels are OV and VDD respectively and I flows only when the input voltage is around the threshold voltage. You will find that the characteristics of a CMOS inverter differ a little from those of a TTL IC.

Fig. 17 CMOS inverter

Fig. 18 CMOS inverter characteristics

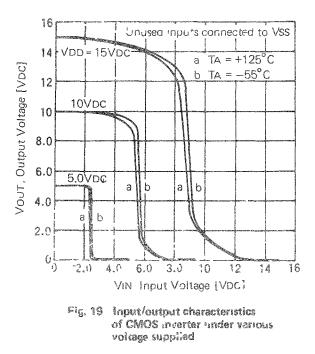

Fig. 19 shows the input-output characteristics of CMOS inverter under various supply voltages. The threshold is always about 1/2VDD.

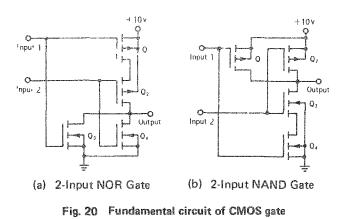

Then how can we make NOR and NAND gates?

Fig. 20 shows funcamental 2-input NOR and 2-input NAND gates. FET's with the same polarity can be piled up without resistors because MOS FET leaves no saturation voltage while it is ON. The inputs can be increased by piling the FET's up. Table 4 shows the function of the NOR gate of Fig. 20 (a).  $Q_1$ ,  $Q_2$ ,  $Q_3$  and  $Q_4$  each works as a switch.

Table 4 Action of 2-input NOR gate "L" = 0V "H" = +10V

| Input 1 | Input 2 | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> | Q <sub>4</sub> | Output |

|---------|---------|----------------|----------------|----------------|----------------|--------|

| L       | L       | ON             | ON             | OFF            | OFF            | Н      |

| L       | Н       | ON             | OFF            | OFF            | ON             | L      |

| н       | L       | OFF            | ON             | ON             | OFF            | L      |

| н       | Н       | OFF            | OFF            | ON             | ON             | L      |

0

#### c) CMOS and TTL

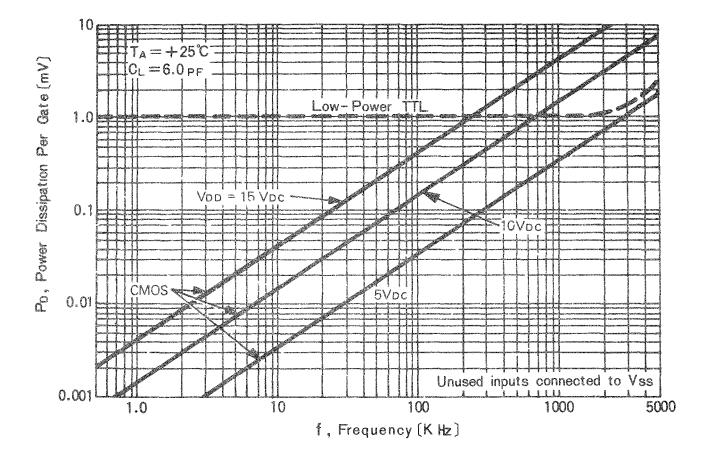

CMOS and TTL are the same from the viewpoint of their logic circuits, but differ in the following points. Fig 21 shows that the power consumption of CMOS gate is very low (about 1/100 that of a TTL gate) at low frequency. Its ID is about  $10^{-9}$ A when its output remains unchanged. The power increases in proportion to frequency because the crossing frequency of fluctuating voltage through the threshold

in a certain period of time increases. Power consumption is important for battery-operated systems. By minimizing heat generation, the integration of largescale circuits and further increasing of reliability are possible. CMOS gates can be operated in the wide power supply range of  $3 \sim 18V$ , while TTL gates function only within the range of  $5V \pm 0.25V$ .

Fig. 21 Power consumption of CMOS gate

CMOS gates have a large noise margin because their threshold is always about 1/2 of the power supply voltage and their logic levels are almost the same as the power supply voltage or the ground level. The noise margin of a CMOS gate is about 45% of the power supply voltage while that of a TTL gate is about 1V. CMOS gates have more than 50 terminals for Fanouts because input current is negligible, while TTL gates of the same family have about 10. However, the number of Fan-outs that can be provided is limited due to wave deformation.

CMOS IC's usually don't employ resistors because transistors can be substituted and are easily integrated into IC's. One slight disadvantage of CMOS gates is their slow response time. The propagation delay time of the MC14001B is 100nS (VDD = 5V) while that of the Texas Instrument's TTL SN7400 is 10nS. So, CMOS gates are operated with a comparatively low clock frequency of about 100kHz.

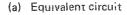

#### d) CMOS switch

A MOS-FET is ideal except for the fact that this has a relatively low maximum input voltage. Fig. 23 shows a bi-directional CMOS switch. When H level voltage is fed to VC, the contact between IN and OUT becomes ON, having a resistance of about  $10^2 \Omega$ in both directions. When VC is at L level, it becomes OFF permitting some current leakage. With this switch, many circuits can be simplified.

Fig. 23 CMOS switch

#### e) Cautions in CMOS IC use

The CMOS IC is electrostatically weak. When it was introduced into the market, it was easily damaged by even rubbing it with a piece of cloth or by operating a piezoelectric cigarette lighter nearby. Because its gate is electronically isolated, being insulated by a thin 1,000Å foi<sup>1</sup>, a leaking AC line voltage generated by a soldering iron may destroy the IC. For protection, the IC should be kept on a piece of conductive sponge or wrapped properly in a piece of aluminum foil.

These conditions apply to NMOS and PMOS IC's. Special care should be taken when handling LSI's, as these are expensive components.

#### 4. Gate combinations

#### 4-1. Advantages of invert-gate circuits

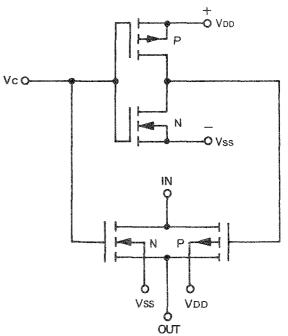

There are many IC's such as NAND and NOR which use inverted logic. Such invert gates are useful when combined with other gates, although they are a little difficult to understand. The main advantage of invert gates is their simplicity. Fig. 24 shows NAND and AND gate circuits. You will see how few elements a NAND gate requires, how little power it consumes and how short its propagation delay time is.

Fig. 24 Circuit of NAND and AND gates

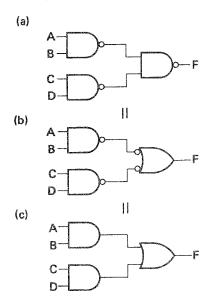

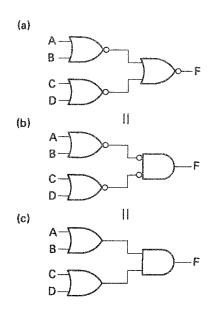

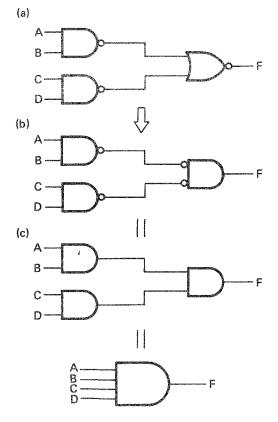

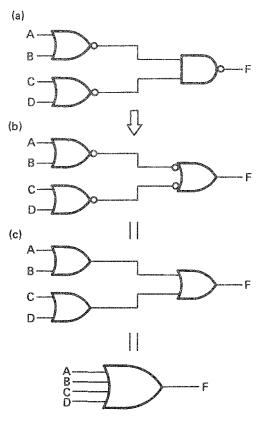

#### 4-2. Multistage gate connections

When gates are to be connected with many steps, it is better to connect them so that power consumption at each step is as low as possible and the total power consumption is kept to a minimum. In addition, from the standpoint of propagation delay, it is better to compose a circuit with invert gates.

Fig. 25 NAND gate combinations

It is easier to understand the logic structure of a circuit if the NAND gates at the output are expressed as Invert OR so that the logic between the steps are made consistent with negative logic.

If the logic throughout a circuit is consistent, whether it is positive or negative, the results will be the same. However, it is also possible for a circuit to use combined logic as in an AND and OR circuit.

Fig. 26 NOR gate combinations

Fig. 27 NAND-NOR connections

Fig. 28 NOR-NAND connections

#### 4-3. Circuit employing gates

#### a) NAND and NOR gates as inverters

Fig. 29 shows one method for making an inverter using NAND and NOR gates. The NAND and NOR truth tables on page 3 explain why they can become an inverter.

This method makes full use of an IC. If a circuit requires three NAND gates and one inverter, it can be made with a NAND IC, which usually consists of four NAND gates, by making a NAND gate into an inverter.

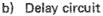

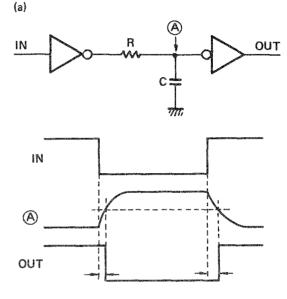

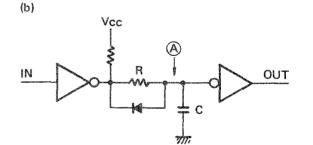

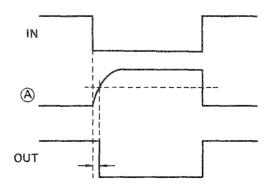

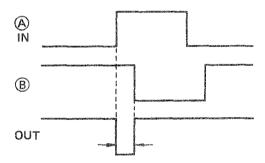

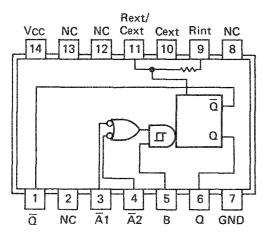

This circuit uses the charging and discharging time of capacitors for delaying output-signal-to-inputsignal response. The delay time is determined by the time constant of C (capacitor) and R (resistor).

In Fig. 30 (a), the time from H to L and from L to H will be delayed in both cases. In (b), the time from H to L will be delayed, however, there will be no time delay from L to H since C is discharging through a diode and not R.

IN OUT IN OUT H IN OUT IN OUT IN OUT

Fig. 29 Using NAND-NOR gate as inverter

Fig. 30 Delay circuit

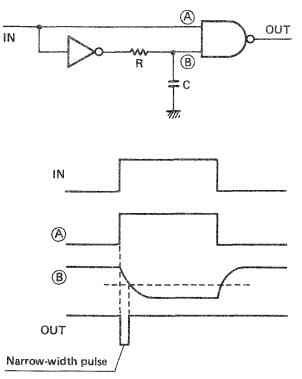

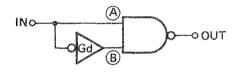

#### c) Trigger pulse generator

In Fig. 31, the inputs of the NAND gate do not coincide. However, this circuit outputs a negative trigger pulse for a short time while the NAND's inputs coincide with the help of the discharging current of C of the delay circuit.

(a)

The circuit in Fig. 32 generates a positive pulse at the rising point of the square wave with two inverters.

Fig. 32 Trigger pulse generator circuit

(b)

Fig. 31 Trigger pulse generator circuit

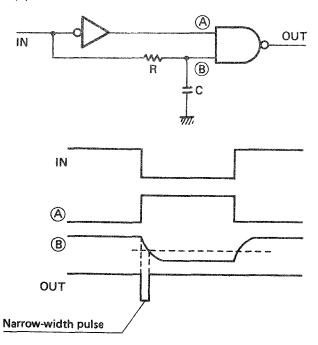

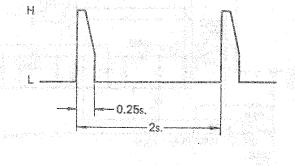

#### d) One-shot (monostable) multivibrator

A monostable multivibrator can be made using two NAND gates or two NOR gates along with capacitors and resistors. This circuit can be easily understood by expressing the first stage gate in OR logic. When the first stage is an Invert OR (NAND) gate, a negative output pulse can be obtained, and when it is a NOR gate, the output pulse is positive. The width of the output pulses will be determined by the time constant of C and R. See Fig. 33

Fig. 33 Monostable multivibrator

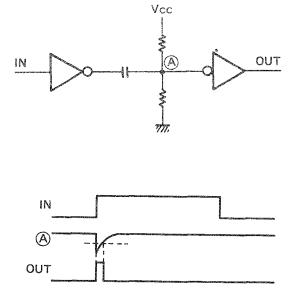

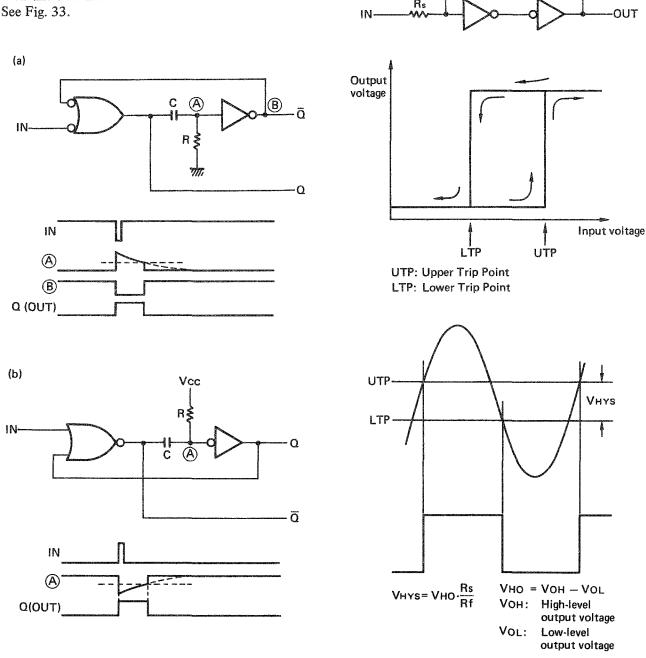

#### e) Schmitt trigger circuit

The Schmitt trigger has a hysteresis input-output characteristic and is used for reshaping the input waveform into a square wave for use in the digital circuit. Hysteresis voltage width can be varied by adjusting Rs and Rf.

R.

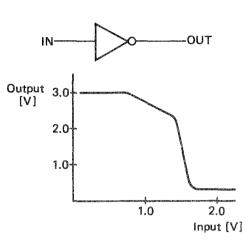

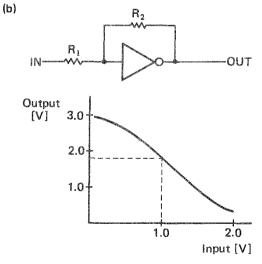

#### f) Linear circuit

The input-output characteristic of an invert gate is nonlinear as shown in Fig. 35 (a). But, by adding a negative feedback resistor as in Fig. 35 (b), more linear characteristics can be achieved. In this way, it can be used as an analog amplifier circuit as well. The gain is expressed: R<sub>2</sub>

This circuit is used in an oscillator circuit which will be explained later.

Fig. 35 Linear circuit

(a)

0

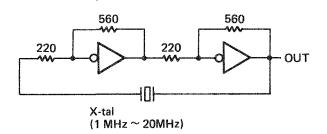

#### h) Quartz oscillator

The capacitor in the feedback stage of the astable multivibrator circuit in Fig. 36 (b) is replaced by a quartz oscillator. The wave form appearing at the output is close to a sine wave, as the oscillating level of the quartz is low-output does not reach saturation level. If a rectangular wave is required, connect a Schmitt trigger circuit shown in Fig. 34 to the output.

Fig. 37 Quartz Oscillator

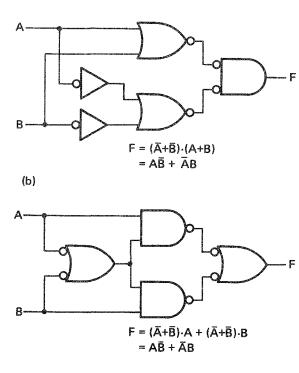

#### i) Exclusive OR circuit

In this circuit, H (1) will appear at the output only when disagreeing signals are fed to the input terminals (A and B). This circuit can be made with invert gates. Fig. 38 (a) shows a circuit employing five NOR gates, while (b) illustrates a four NAND gate circuit (refer to Table 2). The symbol is shown in Fig. 38 (d).

$F = A \oplus B$  stands for  $A\overline{B} + \overline{A}B$ . Therefore,  $A \oplus B = A\overline{B} + \overline{A}B$ .

(a)

#### (c) Truth table

| А     | В | F=A⊕B |  |

|-------|---|-------|--|

| 0     | 0 | 0     |  |

| 0     | 1 | 1     |  |

| 1     | 0 | 1     |  |

| <br>1 | 1 | 0     |  |

(d) Symbol

Fig. 38 Exclusive OR circuit

#### 5. Flip-flop

#### 5-1. Sequential logic circuit

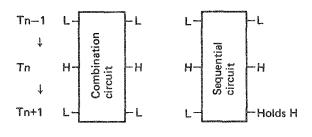

For the digital logic circuits and circuit combinations explained thus far, the only factor which influences signal transmission time is propagation time delay, the same as in the case of analog circuits, otherwise, whenever input is applied, output is obtained at once. However, this is not true with sequential logic circuits where output will not appear unless certain conditions are satisfied. Since the transmission takes time, the output is affected by signal sequence. Flip-flop circuits are typical of this type of logic circuit.

Time sharing is used for transmitting much information on a single channel as digital circuits have limited processing ability in a given time and have to operate signals in order. Their operation also necessitates external circuits. Sequential logic circuits answer such requirements. There are two types of sequential circuits: synchronous and asynchronous. Actually, combination and sequential circuits are used together, rather than separately.

| Tense        | Past | Present | Future |

|--------------|------|---------|--------|

| Digital Term | Tn-1 | Tn      | Tn+1   |

#### Table 5 Tense vs. digital term

This is very convenient in expressing circuit functions sequentially controlled by input signals.

#### 5-2. Fundamental principle of flip-flop circuit

A flip-flop circuit is also called a "bistable multivibrator." The output of a combined circuit varies (L - H - L or H - L - H) in accordance with the variation of its input (L - H - L). By the same input variation, the output of a flip-flop sequential circuit may be shifted from L to H during the time from Tn-1 to Tn. But the H level may be kept unchanged during the time from Tn to Tn+1. This means that the circuit has a memory function for holding the output level from Tn to Tn+1. The output variation of a sequential circuit depends on its composition and the time factor as there are various kinds in the circuits available.

Fig. 39 Combination and sequential circuit output variations based on input

Flip-flop circuits are classified into four types by function:

One-bit memory circuit One-clock pulse delay circuit Binary counter circuit 1/2 frequency divider

#### 5-3. Flip-flops classified by logical function

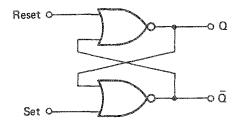

#### a) R-S latch

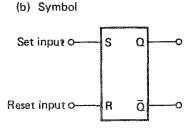

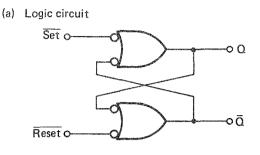

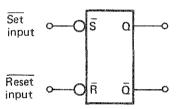

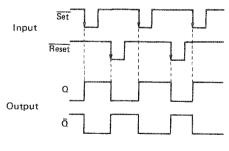

The fundamental sequential logic circuit has two invert gates which are crosscoupled as shown in Fig. 40. A latch is a feedback loop used in a symmetrical digital circuit (such as a flip-flop circuit) to retain a state. It has two input terminals of SET and RESET and has two complementary outputs of Q and  $\overline{Q}$ . The function table for a NOR gate R-S latch is shown in Fig. 40 (c). It is important not to make both the R and S input levels High (1) and then Low (0) simultaneously. As shown in Fig. 40 (c), the outputs do not complement each other when both R-S inputs are H (1). When both R and S inputs shift to L (0), the output levels become indeterminate, although Q and  $\overline{Q}$  are complementary. (a) Logic circuit

| (c) | unction | table |

|-----|---------|-------|

|-----|---------|-------|

| Inp | Input |           | utput |

|-----|-------|-----------|-------|

| S   | R     | Q         | Q     |

| L   | L     | Unchanged |       |

| L   | Н     | L         | Н     |

| н   | L     | н         | L     |

| Н   | Н     | *         | *     |

| . 0 |       |           |       |

\*: Q = Q = L: Inhibition

#### Fig. 40 NOR gate R-S latch

Although Fig. 40 consists of NOR gates, an R-S latch can be made of NAND gates, and expressed by Invert OR circuit as shown in Fig. 41. The R-S latch itself is used as a temporary memory circuit. This is widely applied to complicated flip-flop circuits in combination with control gates and other latches.

(b) Symbol

(c) Function table

| Input |         | Output    |       |

|-------|---------|-----------|-------|

| Ŝ     | R       | Q         | ā     |

| Н     | Н       | Unchanged |       |

| Н     | L       | LH        |       |

| L     | Н       | Н         | L.    |

| L     | L       | *         | *     |

| * Q = | = 0 = H | 1: Inhib  | ition |

(d) Timing chart

Fig. 41 NAND gate R-S latch

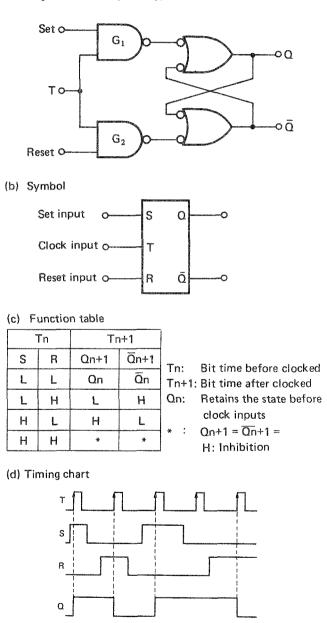

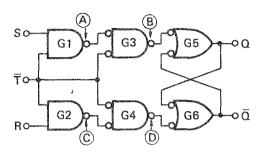

#### b) R-S-T flip-flop (FF)

The Q and Q outputs of an R-S latch vary quickly in accordance with the variation of R-S inputs. When synchronous variation is required to clock signals, a synchronous FF like that shown in Fig. 42 (a), simple R-S-T FF, is employed. This is a doublephase circuit consisting of four NAND gates. Two gates compose an R-S latch. Two other gates,  $G_1$ and  $G_2$  are added to the circuit to synchronize R and S inputs with T. Fig. 42 (c) and (d) show the R-S-T FF's function table and timing chart. When no clock signal is present at T, the outputs of  $G_1$  and  $G_2$  become L and the R-S latch retains its state. When a clock signal appears, R-S inputs are inverted by  $G_1$  and  $G_2$  and then fed to the R-S latch.

With the FF in Fig. 42, Q and  $\overline{Q}$  vary many times with the quick variation of R-S inputs during the period when a clock signal is present.

The synchronous type only changes its output state once with each clock signal. To realize this, it is necessary to narrow down the width of the clock signal. This will be explained later.

#### (a) Logic circuit of 2-phase type R-S-T FF

Fig. 42 R-S-T flip-flop

õ

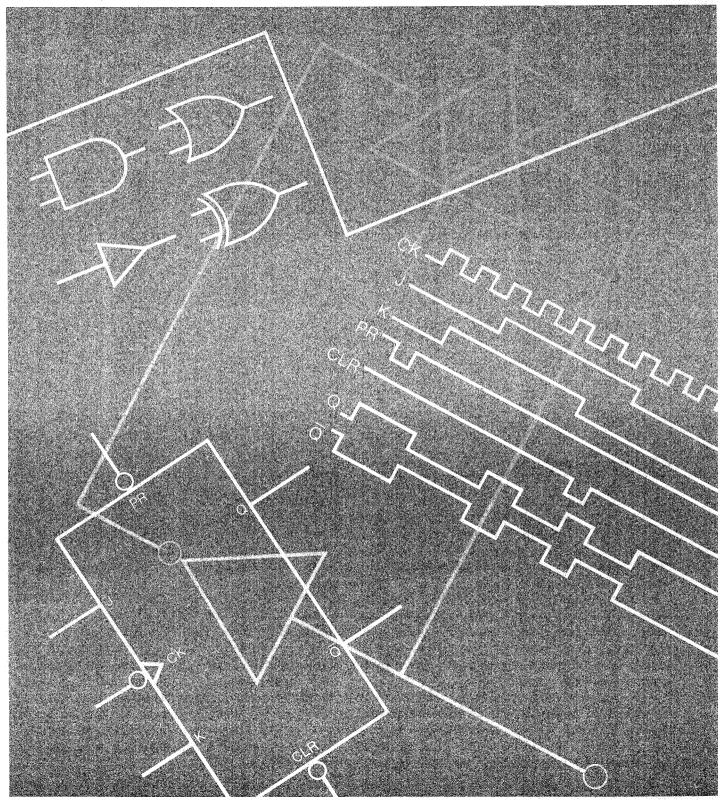

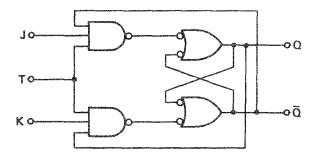

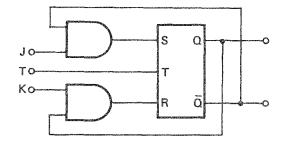

#### c) JK flip-flop

As shown in Fig. 43, a JK FF is also synchronous and has JK inputs instead of R-S inputs like the R-S-T FF. As shown in Fig. 43 (c), the JK flip-flop accepts any input combination. Feeding H to both inputs of an R-S-T FF simultaneously is inhibited, but it is all right with a JK FF because it only inverts the output state of the time before the clock signal is applied.

As shown in Fig. 44, JK FF is basically an R-S-T FF which has been made stable and changes its output state only once with each clock signal. In the JK FF, J input and  $\overline{Q}$  output are fed to SET input, and K input and Q output to RESET input. Thus there is no R:S = H:H input combination for an R-S-T FF.

It should be noted that the circuit may oscillate if the clock signal pulse width is wide.

(a) Logic circuit

(b) Symbol

(c) Function table

| - | Γn | Tn+1 |  |

|---|----|------|--|

| J | к  | Qn+1 |  |

| L | L  | Qn   |  |

| L | н  | L    |  |

| н | L  | н    |  |

| н | н  | Ōn   |  |

Qn: Retains the state before clock inputs  $\overline{Q}n$ : Inverts the state before clock inputs

Fig. 43 JK flip-flop

Fig. 44 JK FF consisting of R-S-T FF

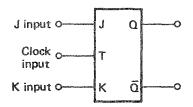

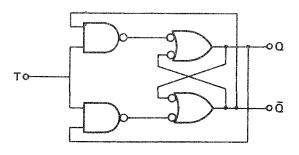

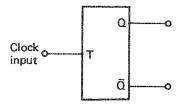

#### d) T flip-flop

With a T FF, the Q and  $\overline{Q}$  outputs change while a clock pulse is present. Therefore, clock pulse width should be narrow as wide pulses cause chattering or frequent switching. The reason and method will be explained in 5-4.

(a) Logic circuit

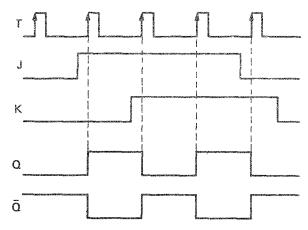

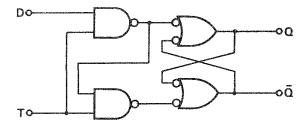

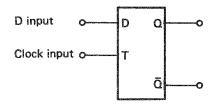

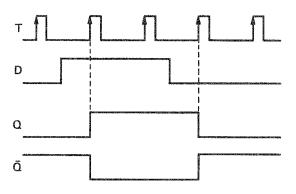

e) D (Delay) flip-flop

As shown in Fig. 46, a D FF has a data input, a clock input and Q and  $\overline{Q}$  outputs. When both D and T are H, Q becomes H and  $\overline{Q}$  becomes L, and when D is L and T is H, Q becomes L and  $\overline{Q}$  becomes H. Thus, signals applied to D appear at the output every time a clock signal is applied.

(a) Logic circuit

(b) Symbol

(c) Function table

| Tn | Tn+1 |

|----|------|

| D  | Qn+1 |

| L  | L    |

| н  | Н    |

(d) Timing chart

Fig. 46 D flip-flop

(b) Symbol

(c) Timing chart

Fig. 45 T flip-flop

#### 5-4. FF's classified by trigger system

As mentioned before, the outputs of a T FF change their state many times during the presence of a clock signal, thus T FF's are liable to oscillate.

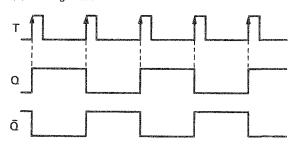

#### a) Edge trigger system

To overcome the oscillation problem, the edgetrigger-very narrow width pulse-system has been developed. This system narrows the clock pulsewidth, reads the input and kills the clock signal immediately after the outputs are changed. In narrowing the clock pulse-width, picking out clock-pulse edges using the gate's propagation delay time is popular, although a different method is used with CR differential circuits.

Pulse width depends on Gd's delay time.

Fig. 47 Edge detection circuit

Gates corresponding to the Gd of Fig. 47 are G1 and G2. The circuit shown in Fig. 48 changes its outputs at the falling, or negative, edge of clock pulses.

Fig. 48 shows an R-S-T FF employing the edge-trigger system.

(a) Logic circuit

Fig. 48 Edge-trigger R-S-T FF

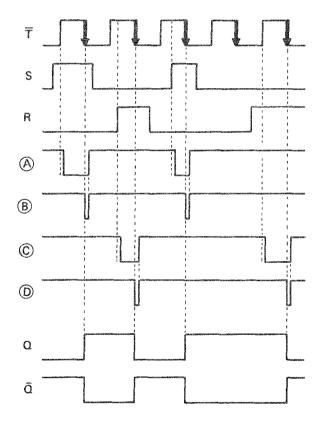

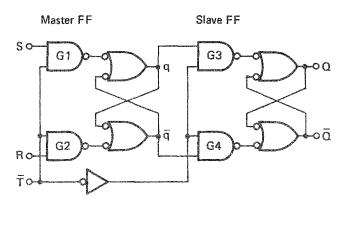

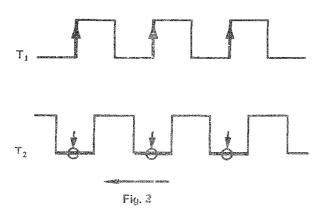

#### b) Master-slave system

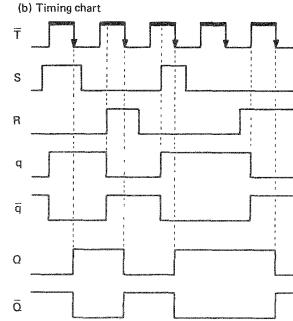

The master-slave system prevents misoperation by varying outputs when the clock signal disappears, while the edge-trigger system prevents frequent output variation by narrowing pulse signal width. This system has two sets of R-S-T FF's which are a master FF and slave FF as shown in Fig. 49. An inverted clock signal is fed to the second FF. When the clock signal is L, L is applied to the input of G1 and G2, and q and  $\overline{q}$  remain unchanged. At this time, an inverted clock signal H is fed to G3 and G4. The states of q and  $\overline{q}$  are then fed into the slave

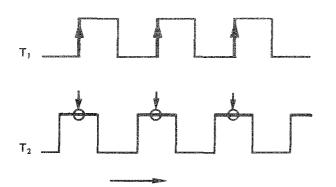

(a) Logic circuit

FF whose signals appear at Q and  $\overline{Q}$ . When the clock signal becomes H, the master FF reads the states of S and R, and outputs q and  $\overline{q}$ . However, Q and  $\overline{Q}$  remain unchanged because G3 and G4 close. When the clock signal changes to L again, the slave FF reads the states of q and  $\overline{q}$  and outputs signals at Q and  $\overline{Q}$ . This means that the outputs vary when the clock signal falls from H to L. Most of the FF IC's on the market are either master-slave or edge-trigger type. The clock input of each can be classified into two types as shown in Table 6.

Fig. 49 Master-slave type R-S-T FF

| Туре         |                           | Logic symbol | Position of clock<br>Input where<br>output shifts | Function of the FF                                                                                                          |

|--------------|---------------------------|--------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Master-slave | Positive going<br>trigger | T            |                                                   | It reads input signal while clock level is L.<br>Output shifts in accordance with function<br>table when clock shifts to H. |

| system       | Negative going<br>trigger |              |                                                   | It reads input while clock level is H. Output<br>shifts in accordance with function table<br>when clock shifts to L.        |

| Edge trigger | Positive going<br>trigger | T            |                                                   | It reads input when clock level shifts to H.<br>Output shifts in accordance with function<br>table at the same time.        |

| system       | Negative going<br>trigger | —            |                                                   | It reads input when clock level shifts to L.<br>Output shifts in accordance with function<br>table at the same time.        |

#### 6. Binary system

#### 6-1. Decimal and binary

To transmit and process data digitally, it is necessary to change it into a form that can be processed by electronic circuits as shown in Fig. 50.

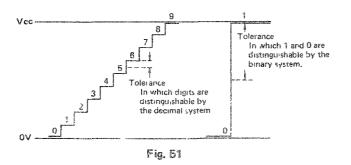

The most appropriate way of handling a large amount of information or data is numerically. Of course, a fixed coding system is required to change one form into another. If we try to introduce decimalization as used in everyday life, we have to divide the limited voltage range into small parts as shown in Fig. 51. This requires ten transfer lines.

Such voltage range division decreases error allowance, and it is not wise to increase the number of transfer lines. A decimal number with the smallest digit called LSD (Least Significant Digit) and the largest, MSD (Most Significant Digit) is weighted by 10, 100, 1,028 and so on.

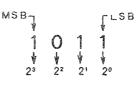

On the other hand, as digits 0 and 1 are used to express any number in the binary system, a carry is made with every odd number. Unlike the everyday decimal system, numbers are expressed in bits (binary digit). As shown in Fig. 53, each of the four bits has a weighting of  $2^{\circ}$ ,  $2^{1}$ ,  $2^{2}$  and  $2^{3}$ , in that order from the smallest bit.

Fig. 52 Weighting of decimal numbers

Fig. 53 Weighting of every bit in the binary system

Table 7 shows the binary equivalents of decimal numbers. Such equivalents are easily obtained when the digits are small, but difficult when they are big. It is useful, therefore, to remember the conversion system for big-digit numbers.

| Decimal | Binary |  |  |

|---------|--------|--|--|

| 0       | 0      |  |  |

| 1       | 1      |  |  |

| -       | -      |  |  |

| 2       | 10     |  |  |

| 3       | 11     |  |  |

| 4       | 100    |  |  |

| 5       | 101    |  |  |

| 6       | 110    |  |  |

| 7       | 111    |  |  |

| 8       | 1000   |  |  |

| 9       | 1001   |  |  |

| 10      | 1010   |  |  |

| 11      | 1011   |  |  |

| 12      | 1100   |  |  |

| 13      | 1101   |  |  |

| 14      | 1110   |  |  |

| 15      | 1111   |  |  |

| •       | ø      |  |  |

| ۵       | ¢      |  |  |

| Ø       | 0      |  |  |

Table 7 Binary equivalents of decimal numbers

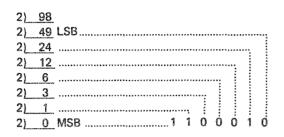

6-2. Decimal/binary and binary/decimal conversion To convert a decimal number to a binary number, the former should be divided by two to the nearest whole digit, as shown in Fig. 54. When the number is divisible, write 0; when it is indivisible and 1 is left, place 1 to the right of the quotient. Then divide the quotient by two again and record a new quotient and residual, until the quotient becomes 0. The residuals obtained represent the binary equivalent of the original decimal number. The first residual (0 is also a residual) is the LSB and the last is the MSB.

Fig. 54 Decimal/binary conversion

As every binary number is weighted as shown in Fig. 53, it can be converted into a decimal number by multiplying each bit's weighting by its value. This is shown in Fig. 55.

1100010 (2) =  $1 \times 2^{6} + 1 \times 2^{5} + 0 \times 2^{4} + 0 \times 2^{3} + 0 \times 2^{2} + 1 \times 2^{1} + 0 \times 2^{0}$ =  $98_{10}$

#### Fig. 55 Binary/decimal conversion

When there are many figures, this method may prove troublesome. In such a case, convert by calculating in groups of four figures each. It is easy to obtain equivalents of four-bit binary numbers as shown in Fig. 56.

|                               | Binary<br>number                                              | Weight                                                                                                                                 |                                                                                                         |

|-------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| MSB<br>Top<br>four<br>figures | $ \left\{\begin{array}{c} 1\\ 0\\ 1\\ 0 \end{array}\right\} $ | $2^{11} = 2^3 \times 2^8$ $2^{10} = 2^2 \times 2^8$ $2^9 = 2^1 \times 2^8$ $2^8 = 2^0 \times 2^8$ $1010(2) = 10(10)$                   | »                                                                                                       |

| Middle<br>four<br>figures     | $ \left\{\begin{array}{c}1\\1\\0\\1\end{array}\right\} $      | $2^{7} = 2^{3} \times 2^{4}$ $2^{6} = 2^{2} \times 2^{4}$ $2^{5} = 2^{1} \times 2^{4}$ $2^{4} = 2^{0} \times 2^{4}$ $1101(2) = 13(10)$ | )) $\left\{ \begin{array}{c} 10 \times 2^{8} + 13 \times 2^{4} + 9 \\ = 2777_{10} \end{array} \right\}$ |

| End<br>four<br>figures<br>LSB | $ \left(\begin{array}{c}1\\0\\0\\1\end{array}\right) $        | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                  |                                                                                                         |

Fig. 56 Binary/decimal conversion

Divide weighting into two stages to obtain four-bit numbers and then convert them into decimal numbers. In the example shown in Fig. 56, multiplying the top four bits by a weighting of  $2^8$ , and the middle four bits by a weighting of  $2^4$  produces the decimal equivalent.

#### 6-3. Binary coded decimal (BCD)

BCD is a code system frequently used for the binary expression of decimal numbers by 1 and 0. Under the system, numbers from 0 to 9 are expressed in four-bit binary numbers as shown in Table 8 (same as ordinary binary equivalents of decimal numbers), and every decimal number is expressed by a four-bit binary number. Binary four-bit numbers can actually represent up to 15 of the decimal system, but combinations for 10 to 15 are not used under the BCD coding system.

| Decimal |   | BC           | D     |       |                |

|---------|---|--------------|-------|-------|----------------|

| Decimal | 8 | 4            | 2     | 1     |                |

| 0       | 0 | 0            | 0     | 0     |                |

| 1       | 0 | 0            | 0     | 1     |                |

| 2       | 0 | 0            | 1     | 0     |                |

| 3       | 0 | 0            | lan a | 1     |                |

| 4       | 0 | Quant        | 0     | 0     |                |

| 5       | 0 |              | 0     | 1     |                |

| 6       | 0 | 1            |       | 0     |                |

| 7       | 0 | dana da      | curds | 1     |                |

| 8       | 1 | 0            | 0     | 0     |                |

| 9       | 1 | 0            | 0     | 4     |                |

| \$      | 1 | 0            | 1     | 0     |                |

| 0       | 1 | 0            | 1     | ş     |                |

| 6       | 1 | <b>A</b> rea | 0     | 0     | Not used under |

| \$      | 1 | T            | 0     | -foon | the BCD system |

| -       | 1 | 1            | -     | 0     |                |

| •       | 1 | 1            | door  | 1     |                |

Table 8 Decimal number/BCD code

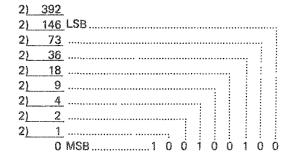

Every bit of a four-bit binary number representing a decimal number has a weighting of 8,4,2 and 1 just like a binary code. In this context, the BCD code system is sometimes called the 8421 code system. Now let's see how the decimal number 392 is expressed in BCD code. The appropriate code can be obtained by writing four-bit binary numbers for each 3, 9 and 2 as shown in Fig. 57 (a). The entire code will thus have 12 bits. For comparison, Fig. 57 (b) shows the conventional binary representation of 392. The binary code, having only nine bits, is quite different from the BCD code.

a) BCD code

b) Conventional binary code

Fig. 57 Difference between BCD and conventional binary codes

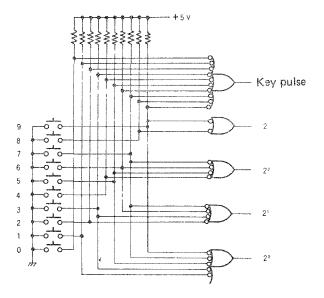

This may give you the impression that the conventional binary code is better and simpler, having less bits. But the reverse is the case. In expressing large decimal numbers by binary codes, the number of bits will increase endlessly, making it very difficult to design a circuit. Although the number of bits for the entire BCD code will also increase, since each decimal digit can be expressed in four bits, a BCD code can be obtained as bit-parallel serial data by using only 10 switches, four transmission lines and several gates, as shown in Fig. 58.

Fig. 58 Decimal-BCD encoder (bit-parallel serial data)

In electric typewriters and electronic calculators, BCD code conversion and operation is carried out by pressing a key switch. An increasing number of measuring instruments, including frequency counters and wow/flutter meters, now have BCD outputs for printers. Other binary coding systems include excess-three code and Gray code systems. However, since these are not generally used, we won't discuss them here.

#### 7. Counter

#### 7-1. Asynchronous binary counter

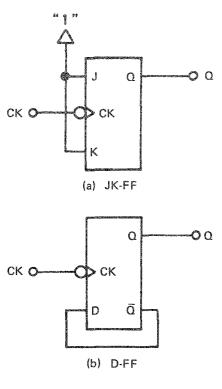

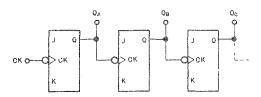

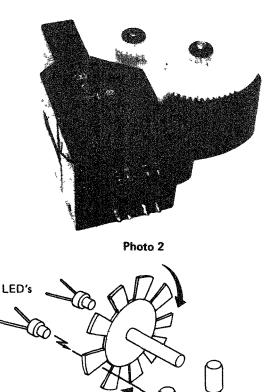

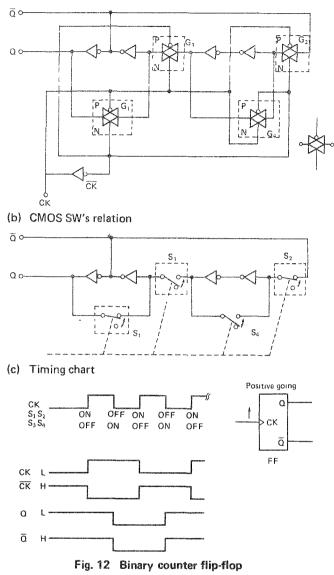

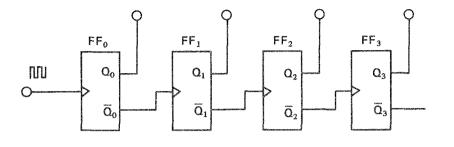

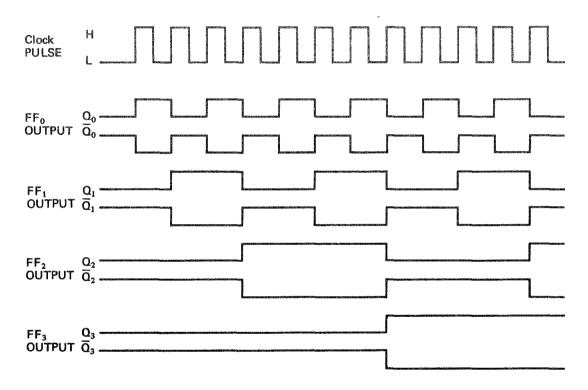

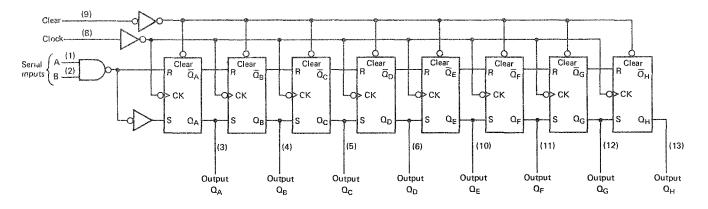

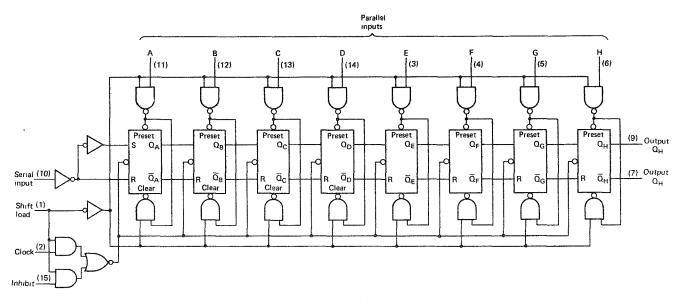

Most digital circuits except AND and OR gates are used as counters, and the asynchronous binary type is the simplest. JK FF or D FF can be wired as shown in Fig. 59 and used in the so-called toggle mode by inverting outputs when the clock pulse falls.

Let us look at the relation between the input clock pulse (CK) and output (Q). If Q was "0" originally, it inverts to "1" when the first pulse falls, and to "0" when the second pulse falls. In the same way it repeats the inversion every time the CK falls. Fig. 59 shows a negative type edge-trigger flip-flop. The positive type works the same as the negative type except that Q inverts when CK rises. These circuits work as 1/2 frequency dividers. You will see in Fig. 60 that they also work as binary counters shifting their outputs to "0" whenever an even number pulse falls and to "1" whenever an odd number pulse falls.

Fig. 59 FF binary counter

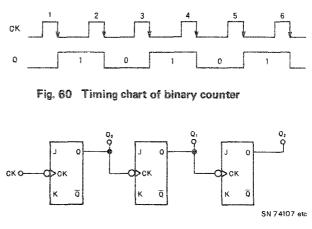

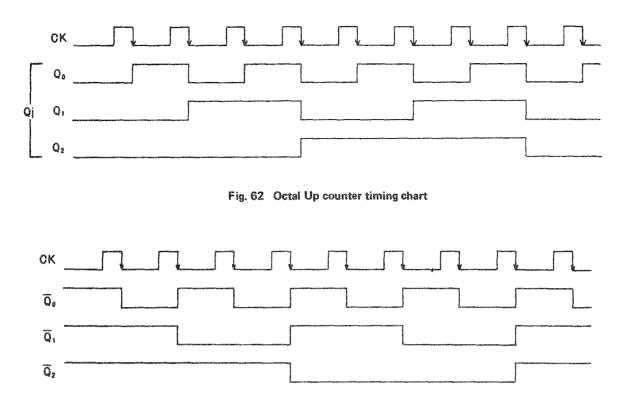

What happens then when the circuits are connected in series as in Fig. 61? The whole circuit becomes a 1/8 frequency divider. If outputs  $Q_0 \sim Q_2$  were 0 originally and were considered to be a three-figure binary number, then the whole circuit would become an octal counter. By connecting units of flip-flops in series, a  $2^n$ -radix (base) counter can be made.

Fig. 61 Asynchronous octal Up counter

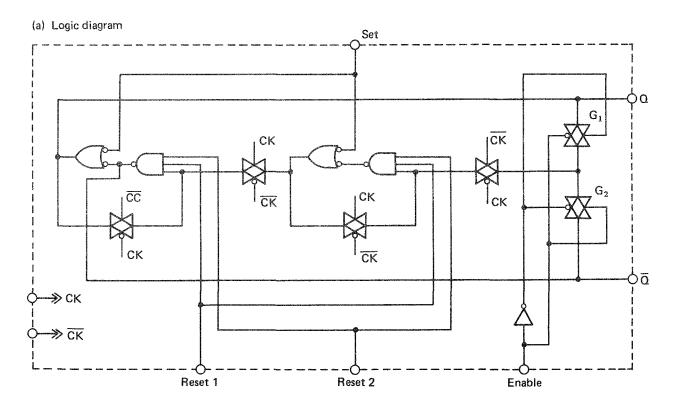

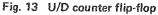

#### 7-2. Up/Down counter

The coded number of the Up counter in Table 9, taken from the Q outputs, increases when clock pulses are fed into the counter (increment). The timing chart of each FF output is shown in Figs. 62 and 63. Conversly, the number of a Down counter taken from  $\overline{Q}$  decreases as pulses are fed (decrement). A Down counter is useful for making a circuit which shifts the function of a device when it has finished counting specified pulses. The octal Up counter in Fig. 62 can be modified to a Down counter by taking the output from  $\overline{Q}$  instead of Q in all cases.

| Output | of | octal | counter |

|--------|----|-------|---------|

|--------|----|-------|---------|

| т                     | Q <sub>2</sub> | Q_1 | Q <sub>0</sub> | decimal |

|-----------------------|----------------|-----|----------------|---------|

| To                    | 0              | 0   | 0              | 0       |

| T <sub>1</sub>        | 0              | 0   | 1              | 1       |

| $T_2$                 | 0              | 1   | 0              | 2       |

| T <sub>3</sub>        | 0              | 1   | 1              | 3       |

| T4                    | 1              | 0   | 0              | 4       |

| $T_5$                 | 1              | 0   | 1              | 5       |

| $T_6$                 | 1              | 1   | 0              | 6       |

| <b>T</b> <sub>7</sub> | 1              | 1   | 1              | 7       |

| $T_8$                 | 0              | 0   | 0              | 0       |

| T9                    | 0              | 0   | 1              | 1       |

| ۲                     |                |     |                |         |

| ۲                     |                |     |                |         |

|                       |                |     |                |         |

Table 9 Table of octal counter (T: number of pulses)

Fig. 63 Octal Down counter timing chart

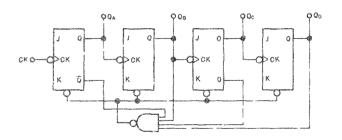

#### 7-3. N-radix system

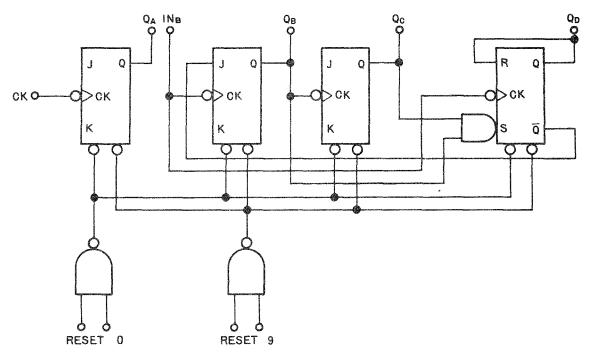

What about making decimal and duo-decimal counters? A simple method is to count up from 1 to 10, sense it, and then clear all flip-flops. Fig. 64 shows a decimal counter. The binary code expression of decimal 10 is "1010". A four-input NAND gate senses the number "1010" and clears all flipflops. To make a N-radix counter, N units of flipflops which satisfy the following formula are required. n

$$2^{n-1} < N \le 2^{r}$$

Fig. 65 shows a TTL-MSI decimal counter. The circuit can use a manipulate method as a binaryquinary or a quinary-binary counter and has terminals for resetting to 0 or 9.

When using this circuit as a binary-quinary counter, its output becomes BCD.

Fig. 64 Asynchronous decimal counter

Fig. 65 MSI decimal counter SN7490

#### 7-4. Synchronous counter

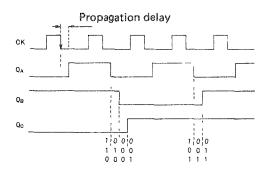

All the counters explained so far are asynchronous type (Ripple counter). Time lag between input and output signals are inherent to the flip-flop used. A TTL's time lag is 10–30ns. The more stages, the longer the delay becomes. This presents a problem when using the counter as a timing device and connecting more than two outputs except when

Fig. 66 Asynchronous counter propagation delay

Fig. 67 Timing chart of asynchronous counter

using it as a frequency divider. As shown in Fig. 67, even an octal counter gives undesirable output codes such as  $011 \rightarrow 010 \rightarrow 000 \rightarrow 100$  during the time that CK is fed to the input until the output stabilizes. The incorrect output causes the trigger circuits to malfunction. To prevent this, it is necessary to make the CK level of every flip-flop invert at the same time.

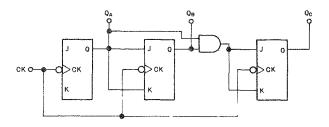

A synchronous counter solves the problem. These vary in composition. The principle, however, is the same as that of asynchronous counters. The output of the counter is inverted when the outputs of all preceding flip-flops are 1. Synchronous counters are more complicated than asynchronous ones. Fig. 68 shows a synchronous type octal counter. You will notice that all flip-flops are controlled by the same clock pulse synchronoulsy.

Fig. 68 Synchronous octal counter

#### 7-5. MSI counter

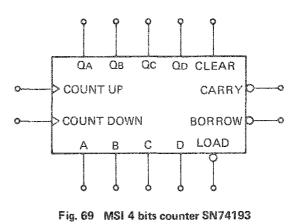

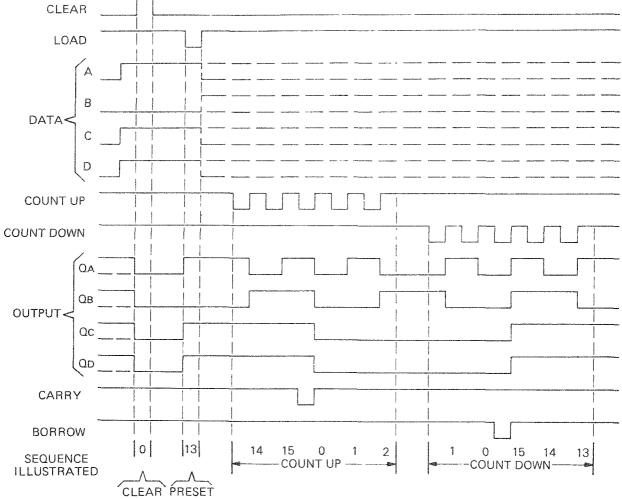

Usually, separate flip-flops are not used for counters since MSI's (Middle Scale Integration) have become readily available. Figs. 69 and 70 show an MSI counter. This is a synchronous type and is capable of both count-up and count-down functions. This is a 4-bit (a 4 flip-flop) counter and is capable of binary-hexadecimal counting by using asynchronous Clear (which makes all flip-flops "0") and Load (which gives flip-flops original values) for carry, borrow and clear. Further, counting more than 16 is possible by connecting carry (borrow) to count up (count down). But, it should be noted that each MSI works asynchronously in this case.

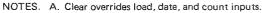

#### 7-6. Decoder circuit

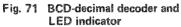

The output codes of counters or signal lines are mostly binary or similar to binary. Decoding binary values is necessary as it is hard to read them. Decoder IC's are available, although you can design a decoder by yourself by combining a number of gates. The indicator in Fig. 71 lights an LED which corresponds to the input code. The block diagram of an SN7445 is shown in Fig. 72, while its function table appears in Table 10.

B. When counting up, count-down input must be high; when counting down, count-up input must be high.

Fig. 70 Timing chart of SN74193

| NO      |       | Inp  | ut  |       |      |      |     | (   | Out | put |   |   |   |   |

|---------|-------|------|-----|-------|------|------|-----|-----|-----|-----|---|---|---|---|

| NO.     | D     | С    | в   | А     | 0    | 1    | 2   | 3   | 4   | 5   | 6 | 7 | 8 | 9 |

| 0       | L     | L    | L   | L     | L    | L    | Н   | Н   | Н   | Н   | Н | Н | Н | Н |

| 1       | L     | L    | L   | Н     | н    | NCH2 | Н   | Н   | Н   | Н   | Н | Н | Н | Н |

| 2       | L     | L    | Н   | L     | н    | Н    | L   | Н   | Н   | Н   | Н | Н | Н | Н |

| 3       | L     | L    | Н   | Н     | н    | Н    | Н   | L   | Н   | Н   | Н | Н | Н | Н |

| 4       | L     | Н    | L   |       | н    | Н    | Н   | Н   | L   | Н   | Н | Н | Н | Н |

| 5       | L     | Н    | L.  | Н     | н    | Н    | Н   | Н   | Н   | L   | H | Н | Н | Н |

| 6       | L     | Н    | Н   | L     | н    | Η    | Н   | Н   | Н   | Н   | L | Н | Н | Н |

| 7       | 1     | Н    | Н   | Н     | Н    | Н    | Н   | Н   | Н   | Н   | Н | L | Н | Н |

| 8       | Н     | L    | L   | L     | н    | Н    | Н   | Н   | н   | Н   | Н | Н | L | Н |

| 9       | Η     | L    | L   | Н     | н    | Н    | Н   | Н   | Н   | Н   | Н | Н | Н | L |

|         | Н     | L    | Н   | L     | Н    | Н    | Н   | н   | Н   | Н   | Н | Н | Н | Н |

|         | н     | L    | Н   | Н     | Н    | Н    | Н   | Н   | Н   | Н   | Н | Н | Н | Н |

| lid     | Н     | Н    | L   | L     | н    | Н    | Н   | Н   | Н   | Н   | Н | Н | Н | Н |

| Invalid | н     | Н    | L   | Н     | н    | Н    | Н   | Н   | Н   | Н   | Н | Н | Н | Н |

| -       | н     | Н    | Н   | L     | н    | Н    | Н   | Н   | Н   | Н   | н | Н | Н | Н |

|         | н     | Н    | Н   | Н     | н    | Н    | Н   | Н   | Н   | Н   | Н | Н | Н | Н |

| H = hig | h lev | el ( | OFF | =). L | = 10 | w le | vel | (ON | 1)  |     |   |   |   |   |

Table 10 Function table of SN7445

Fig. 72 Functional block diagram for SN7445

1

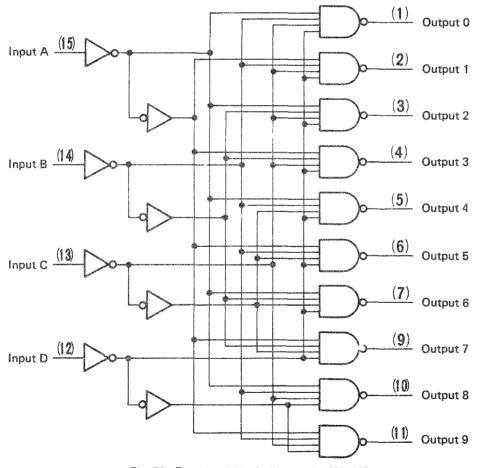

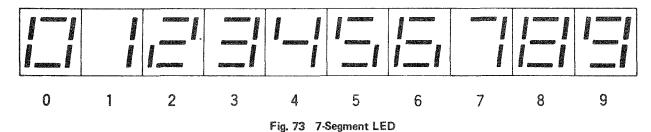

A 7-segment decoder turns LED's on and off to form figures as shown in Fig. 73. IC's SN7446  $\sim$  49 have this function. Some decoders have an ENABLE input as shown in Fig. 74 which allows all outputs second adjustment. O-second setting can be made by pressing the "O-second Set" switch and clearing the second counter until the correct second appears. Fig. 75 shows the block diagram of a digital clock.

to be turned off. The decoder is sometimes called a Data Demultiplexer because of its switching function which conveys ENABLE input to a specified output terminal.

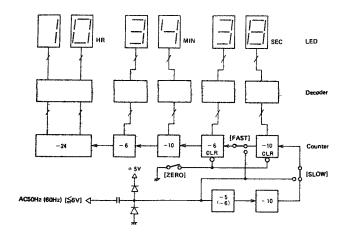

#### 7-7. Counter circuit application (clock)

The counter circuit is popularly applied to digital clocks, which work by counting pulses of a reference frequency. If the line frequency is 60Hz, one second can be recognized by counting 60 peaks of the alternating current, one minute by counting 60 seconds, and so on. Time indication can be done with 7-segment LED's and an exclusive decoder. What about time setting? Most of the digital clocks on the market go fast-forward when a time setting switch is pressed. To make the time setting speed up, it is necessary to make the reference clock frequency higher than 60Hz. By making the clock signal bypass the 1-second divider, time setting is speeded up by 60 times. Even so, it would still take 20 minutes to advance the time for 24 hours. To make it advance still faster, the 10-minute frequency divider is also bypassed. Thus the 1-second frequency divider bypassing switch is used for "slow" adjustment and the 10-minute frequency divider bypassing switch for "fast" mode.

This way, it only takes a little more than two minutes to make a full 24-hour adjustment. However, these fast-forward switches cannot make

Fig. 74 Decoder with enable terminal (de-multiplexer)

The counter can be asynchronous. An SN7490 can be used for a quinary-decimal counter and an SN7492 for a hexal type. Making a 24-radix counter only is meaningless, since BCD output is necessary for indicating time. The output can be made with the remaining binary counter portions of the SN7490 and SN7492 along with one or two gates.

Fig. 75 Block diagram of digital clock

## Application Course (1) CT-F750

**1. Control Circuit's Functions**

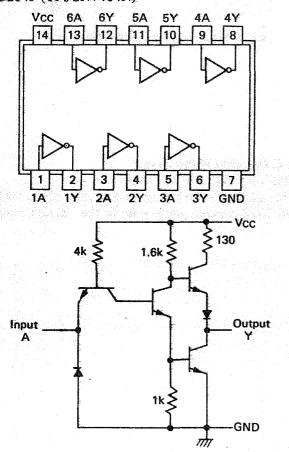

1-1. IC's employed Inverter M53204P (TI's SN7404N)

Fig. 1 Inverter M53204P (SN7404N)

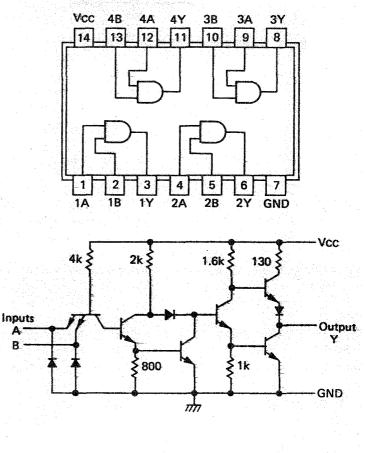

AND M53208P (TI's SN7408N)

Fig. 2 AND Circuit M53208P (SN7408N)

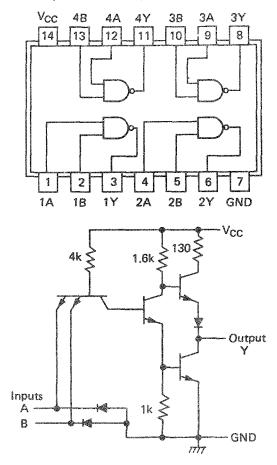

#### NAND M53200P (TI's SN7400N)

Fig. 3 NAND Circuit M53200P (SN7400N)

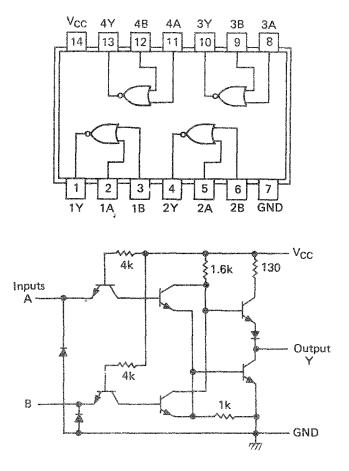

#### NOR M53202P (TI's SN7402N)

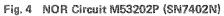

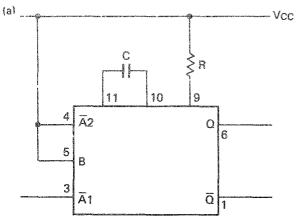

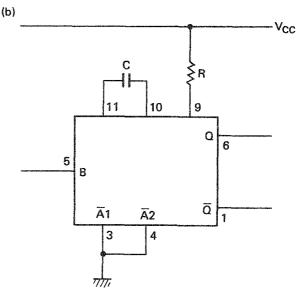

1-2. One-shot Multivibrator M53321P (II's SN74121N) For detailed descriptions of Inverter, AND, NAND and NOR circuits. please refer to the "Basic Course." **1-3. One-Shot Multivibrator M53321P's functions** This One-Shot Multivibrator puts out a pulse signal when certain input conditions are satisfied. The pulse width of the M53321P can be adjusted by varying the value of the external capacitor and resistor.

Fig. 5 Pin alignment and block diagram

|    | Inputs | na fan de fan de fersen en de fersen fersen en de fersen fersen en de fersen en de fersen en de fersen en de fe | Outp     | outs                                                                                                            |

|----|--------|-----------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------|

| Ā1 | Ā2     | В                                                                                                               | ٩        | ā                                                                                                               |

| L  | Х      | Н                                                                                                               | L        | Н                                                                                                               |

| x  | L.     | Н                                                                                                               | L        | Н                                                                                                               |

| x  | Х      |                                                                                                                 | <b>.</b> | н                                                                                                               |

| H  | H      | Х                                                                                                               |          | Н                                                                                                               |

| н  | ł      | Н                                                                                                               |          |                                                                                                                 |

| 4  | ĸ      | Н                                                                                                               | _TL      |                                                                                                                 |

| ł  | Ļ      | Н                                                                                                               |          | and the second                                                                                                  |

| L  | Х      | Ŧ                                                                                                               |          |                                                                                                                 |

| х  |        | 4                                                                                                               | L.       |                                                                                                                 |

|    | Fig. 6 | Functio                                                                                                         | on table | in The second |

There are two ways of connecting the M53321P as shown in Fig. 7:

Fig. 7 Connections of M53321P

Fig. 7(a): Terminals 4 ( $\overline{A}2$ ) and 5 (B) are connected to Vcc which is H level. Now, refer to the function table in Fig. 6. ( $\overline{A}2$ ) and B are always H and only when the level at 3 ( $\overline{A}1$ ) falls to L, output 6 (Q) inverts from L to H and then returns to L after a certain period of time. A positive pulse can be obtained at Q; the pulse width is determined by the product value of the capacitor and resistor connected to the IC. The actual time constant value is different from the product value because the IC has an internal resistor. The pulse width will be explained later. The level of  $\overline{Q}$  is always opposite to that of Q (refer to "Basic Course" Section on flip-flops).

Fig. 7 (b): Terminals 3 ( $\overline{A}1$ ) and 4 ( $\overline{A}2$ ) remain L because they are grounded. Refer to the Function Table in Fig. 6. "X" means that the level can be either H or L. Since  $\overline{A}1$  and  $\overline{A}2$  are always L, a positive pulse and a negative pulse appear at 6 (Q) and 1 ( $\overline{Q}$ ) respectively only when the level at 5 (B) rises to H. In almost all cases, the outputs of 6 (Q) and 1 ( $\overline{Q}$ ) remain unchanged in respect to L and H, except in the following instances:

When input at 3 ( $\overline{A}$ ) shifts from H to L in the circuit in Fig. 7 (a).

When input at 5 (B) shifts from L to H in the circuit in Fig. 7 (b).

In each case, a pulse of a certain width appears at the output terminals, a positive pulse at 6 and a negative pulse at 1.

#### 2. Circuit Description

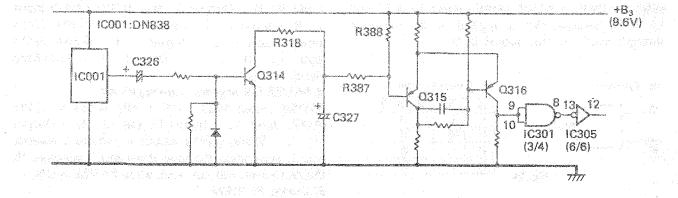

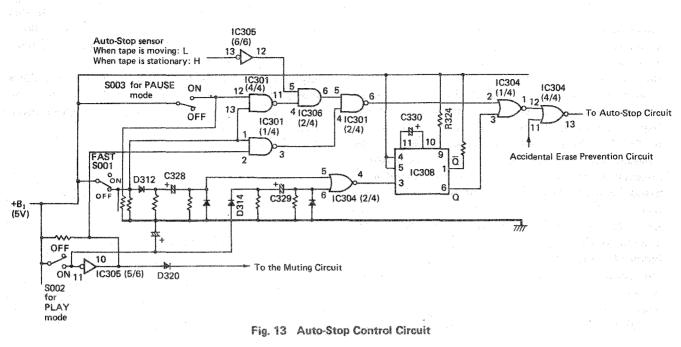

2-1. Auto-Stop Circuit (solenoid activation)

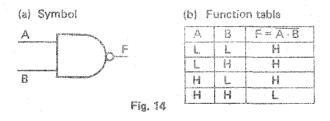

(b) Function table (a) Symbol F = A + BB Δ А H --1 and a 5 -1 8 R ages .

#### Fig. 9

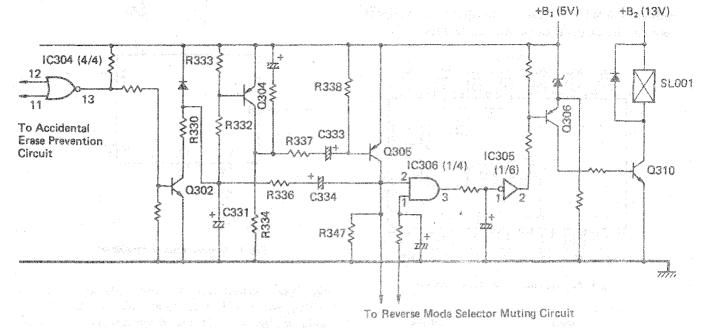

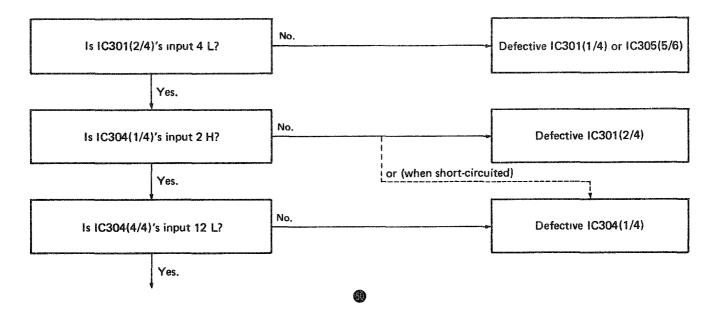

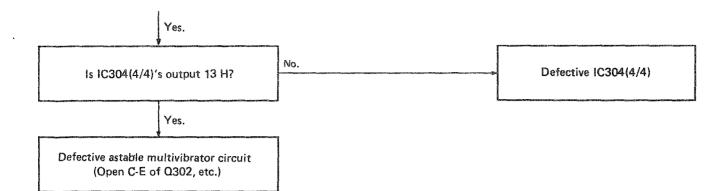

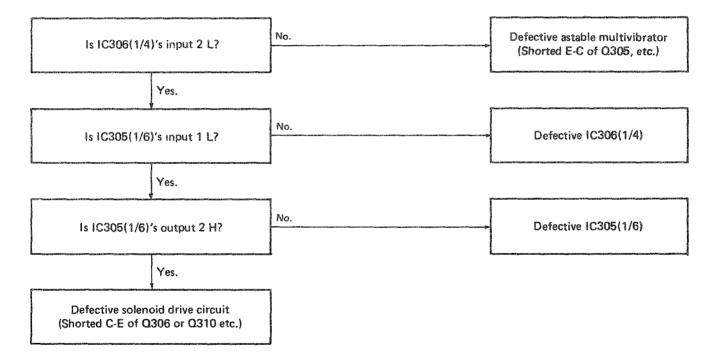

When in the PLAY mode and PAUSE is pressed, inputs 11 and 12 of IC304 (4/4)'s NOR gate are L and output 13 becomes H (refer to Fig. 9). IC304 (4/4)'s output at 13 :  $H \rightarrow Q302$ 's base :  $H \rightarrow Q302$  :  $ON \rightarrow$ Current flows from +B1 through R333, R332, R330 and Q302  $\rightarrow$  Q304's base :  $L \rightarrow Q304$  :  $ON \rightarrow$ Collector :  $H \rightarrow C333$ 's terminals almost equal to +B1  $\rightarrow$  No current through R338  $\rightarrow$  Q305's base :  $H \rightarrow$ Q305 : OFF  $\rightarrow$  IC306 (1/4)'s input 2 :  $L \rightarrow$  Output 3 : L (refer to Fig. 10)  $\rightarrow$  IC305 (1/6) inverts L

(b) Function table

| A  | В | $F = A \cdot B$ |

|----|---|-----------------|

| L  | L | L.              |

| ·L | Н | L               |

| Н  | Ŀ | L               |

| Н  | Н | Н               |

Fig. 10

Fig. 8 Auto-Stop Circuit

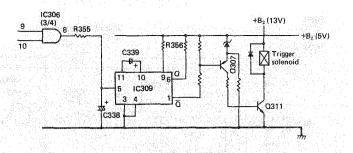

to  $H \rightarrow Q306$ 's base :  $H \rightarrow Q306$  : OFF  $\rightarrow Q310$ 's base :  $L \rightarrow Auto-Stop$  solenoid SL001 is not activated (PLAY or PAUSE).

At the end of PLAY, FF, REW or when the Accidental Erase Prevention Circuit is activated (explained later), input 11 or 12 of NOR IC304 (4/4) becomes H and output 13 becomes L.

IC304 (4/4)'s output 13 :  $L \rightarrow Q302$ 's base :  $L \rightarrow Q302$  : OFF  $\rightarrow$  C331 is charged through R333 and R332  $\rightarrow$  Charging completed  $\rightarrow$  Current stops  $\rightarrow$  Q304's base:  $H \rightarrow Q304$  : OFF  $\rightarrow$  C333 is charged through R338, R337 and R334  $\rightarrow$  Q305's base :  $L \rightarrow$  Q305 : ON  $\rightarrow$  IC306 (1/4)'s input 2 : H. When tape stops, except when auto-reversing, (explained later) input 1 of IC306 (1/4) is H  $\rightarrow$  Both inputs 1 & 2 : H  $\rightarrow$  Output 3 : H  $\rightarrow$  Inverter IC305 (1/6)'s output : L  $\rightarrow$  Q306's base :  $L \rightarrow$  Q306 : ON  $\rightarrow$  Q310's base : H  $\rightarrow$  Q310 : ON  $\rightarrow$  Auto-Stop solenoid activated, tape transport stops.

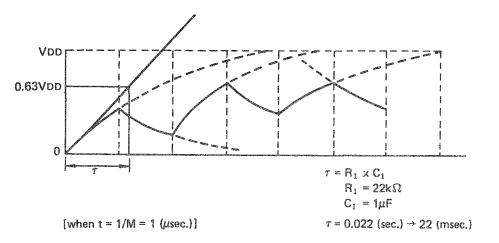

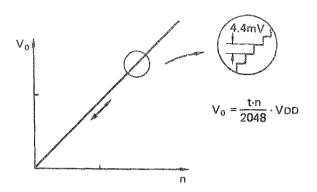

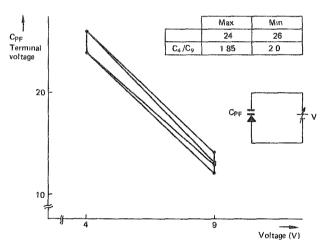

#### Role of astable multivibrator

In the normal state, the Auto-Stop solenoid becomes activated when an L signal from IC304 (4/4)is inverted and fed to input 2 of IC306 (1/4).